- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376460 > XRT7245 (Exar Corporation) DS3 ATM User Network Interface(DS3異步傳輸模式用戶網(wǎng)絡(luò)接口) PDF資料下載

參數(shù)資料

| 型號(hào): | XRT7245 |

| 廠商: | Exar Corporation |

| 英文描述: | DS3 ATM User Network Interface(DS3異步傳輸模式用戶網(wǎng)絡(luò)接口) |

| 中文描述: | DS3自動(dòng)柜員機(jī)用戶網(wǎng)絡(luò)接口(DS3異步傳輸模式用戶網(wǎng)絡(luò)接口) |

| 文件頁數(shù): | 275/324頁 |

| 文件大?。?/td> | 4103K |

| 代理商: | XRT7245 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁第179頁第180頁第181頁第182頁第183頁第184頁第185頁第186頁第187頁第188頁第189頁第190頁第191頁第192頁第193頁第194頁第195頁第196頁第197頁第198頁第199頁第200頁第201頁第202頁第203頁第204頁第205頁第206頁第207頁第208頁第209頁第210頁第211頁第212頁第213頁第214頁第215頁第216頁第217頁第218頁第219頁第220頁第221頁第222頁第223頁第224頁第225頁第226頁第227頁第228頁第229頁第230頁第231頁第232頁第233頁第234頁第235頁第236頁第237頁第238頁第239頁第240頁第241頁第242頁第243頁第244頁第245頁第246頁第247頁第248頁第249頁第250頁第251頁第252頁第253頁第254頁第255頁第256頁第257頁第258頁第259頁第260頁第261頁第262頁第263頁第264頁第265頁第266頁第267頁第268頁第269頁第270頁第271頁第272頁第273頁第274頁當(dāng)前第275頁第276頁第277頁第278頁第279頁第280頁第281頁第282頁第283頁第284頁第285頁第286頁第287頁第288頁第289頁第290頁第291頁第292頁第293頁第294頁第295頁第296頁第297頁第298頁第299頁第300頁第301頁第302頁第303頁第304頁第305頁第306頁第307頁第308頁第309頁第310頁第311頁第312頁第313頁第314頁第315頁第316頁第317頁第318頁第319頁第320頁第321頁第322頁第323頁第324頁

á

PRELIMINARY

DS3 UNI FOR ATM

XRT7245

REV. 1.03

275

Note:

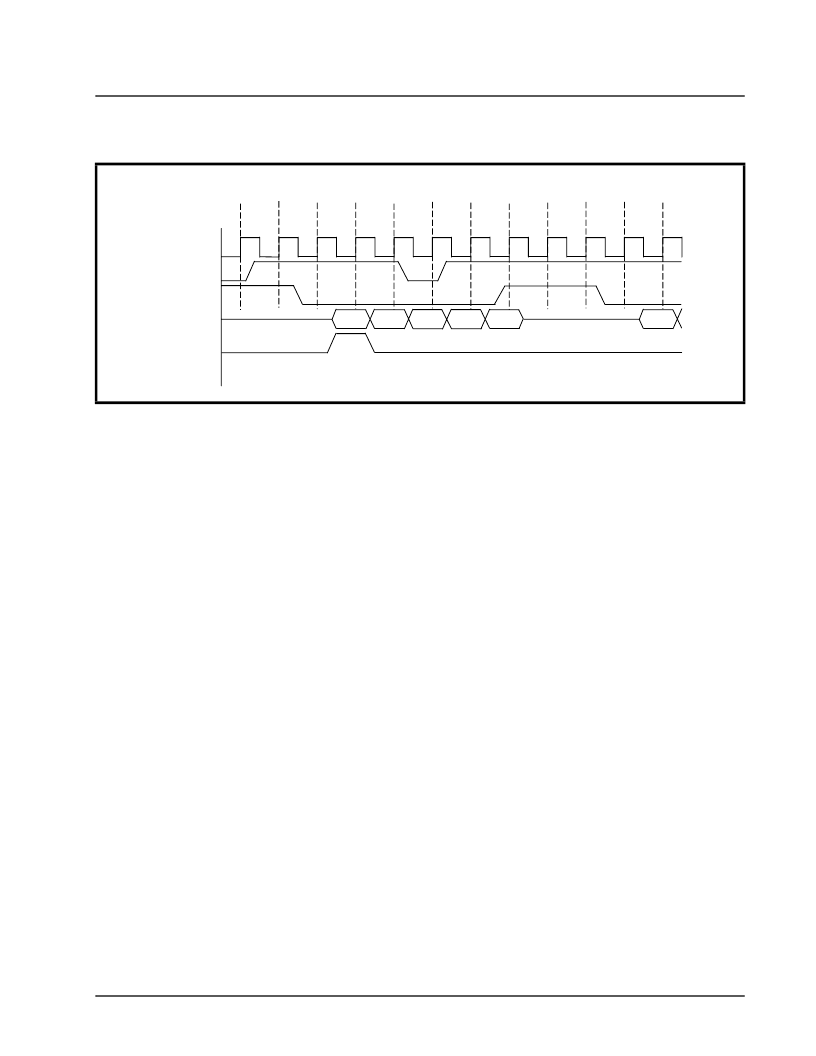

regarding Figure 86

1. The Receive UTOPIA Data bus is configured to be

16 bits wide. Hence, the data which the Receive

UTOPIA Interface block places on the Receive

UTOPIA Data bus is expressed in terms of 16 bit

words (e.g., W0–W26).

2. The Receive UTOPIA Interface block is configured

to handle 54 bytes/cell. Hence, Figure 86 illustrates

the ATM Layer processor reading 27 words (W0

through W26) for each ATM cell.

In Figure 86, RxClav is initially “l(fā)ow” during clock edge

#1. However, shortly after clock edge 1, the RxFIFO

receives ATM cell data from the Receive Cell Processor

block. At this point, the RxClav signal toggles “high”

indicating that the RxFIFO contains at least one

“read-cycle” worth of cell data. The ATM Layer pro-

cessor will detect this “assertion of RxClav” during

clock edge #2. Consequently, in order to begin read-

ing this cell data, the ATM Layer processor will then

assert the RxEnB* input pin. At clock edge #3, the

Receive UTOPIA Interface block detects RxEnB*

being “l(fā)ow”. Hence, the Receive UTOPIA Interface

block then places word W0 on the Receive UTOPIA

Data bus. The ATM Layer processor latches and

reads in W0, upon clock edge #4. In this figure,

shortly after the ATM Layer processor has read in

word W1 (at clock edge #5), the RxFIFO is depleted

which causes RxClav to toggle “l(fā)ow”. In this figure,

the ATM Layer processor will keep the RxEnB* signal

asserted, and will read in an “invalid” word which is

denoted by the “X” in Figure 86. Shortly thereafter,

the RxFIFO receives some additional cell data from

the Receive Cell Processor, which in turn causes

RxClav to toggle “high”. The ATM Layer processor

then continues to read in words W2 and W3. After-

wards, the ATM Layer processor is unable to continue

reading the ATM cell data from the Receive UTOPIA

Interface block; and subsequently negates the RxEnB*

signal; at clock edge #8. The Receive UTOPIA Inter-

face block detects that RxEnB* is “high” at clock edge

#8, and in turn, tri-states the Receive UTOPIA Data

Bus at around clock edge # 9. Finally, prior to clock

edge #11, the ATM Layer processor is able to resume

reading in ATM cell data from the Receive UTOPIA

Interface block, and indicates this fact by asserting

the RxEnB* (e.g., toggling it “l(fā)ow”). The Receive

UTOPIA Interface block detects this state change at

clock edge #11 and subsequently places word W4 on

the Receive UTOPIA Data bus.

7.4.2.2.1.2

The UNI will be operating in the “Cell-Level” Hand-

shaking mode following power up or reset. In the

“Cell-Level” Handshaking mode, when the RxClav

output is at a logic “1”, it means that the Rx FIFO

contains at least one complete ATM cell of data that

is available for reading by the ATM Layer Processor.

When RxClav toggles from “high” to “l(fā)ow”, it indicates

that Rx FIFO contains less than one complete ATM

cell. As in the “Octet-Level” Handshake mode, the ATM

Layer processor is expected to monitor the RxClav

output, and quickly respond and read the Rx FIFO,

whenever the RxClav output signal is asserted.

The UNI can operate in either the “Octet-Level” or

“Cell-Level” Handshake mode, when operating in the

Single-PHY mode. However, only the Cell-Level

Handshake Mode is available when the UNI is oper-

ating in the Multi-PHY mode. For more information on

Single PHY and Multi PHY operation, please see

Section 7.4.2.2.2.

Cell Level Handshaking

F

IGURE

86. T

IMING

D

IAGRAM

OF

R

X

C

LAV

/R

X

E

MPTY

B

AND

VARIOUS

OTHER

SIGNALS

DURING

READS

FROM

THE

R

ECEIVE

UTOPIA,

WHILE

OPERATING

IN

THE

O

CTET

-L

EVEL

H

ANDSHAKING

M

ODE

.

RxClk

RxClav

RxEnB*

RxData[15:0]

RxSoC

W2

W3

W4

X

W1

W0

1

2

3

4

5

6

7

8

9

10

11

12

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XRT7288IP | CEPT1 Line Interface |

| XRT7288 | CEPT1 Line Interface(CEPT1線接口) |

| XRT7288IW | CEPT1 Line Interface |

| XRT7295AE | E3 (34.368Mbps) Integrated line Receiver |

| XRT7295AE_03 | E3 (34.368Mbps) Integrated line Receiver |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XRT7250 | 制造商:EXAR 制造商全稱:EXAR 功能描述:DS3/E3 FRAMER IC |

| XRT7250ES-PCI | 功能描述:界面開發(fā)工具 Evaluation Board for XRT7250 Series RoHS:否 制造商:Bourns 產(chǎn)品:Evaluation Boards 類型:RS-485 工具用于評估:ADM3485E 接口類型:RS-485 工作電源電壓:3.3 V |

| XRT7250IQ100 | 制造商:EXAR 制造商全稱:EXAR 功能描述:DS3/E3 FRAMER IC |

| XRT7288 | 制造商:EXAR 制造商全稱:EXAR 功能描述:CEPT1 Line Interface |

| XR-T7288 | 制造商:EXAR 制造商全稱:EXAR 功能描述:CEPT1 Line Interface |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。