- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370261 > FW82815 Controller Miscellaneous - Datasheet Reference PDF資料下載

參數(shù)資料

| 型號: | FW82815 |

| 英文描述: | Controller Miscellaneous - Datasheet Reference |

| 中文描述: | 控制器雜項-數(shù)據(jù)表參考 |

| 文件頁數(shù): | 8/172頁 |

| 文件大小: | 795K |

| 代理商: | FW82815 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁當前第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁

82815 GMCH

R

8

Datasheet

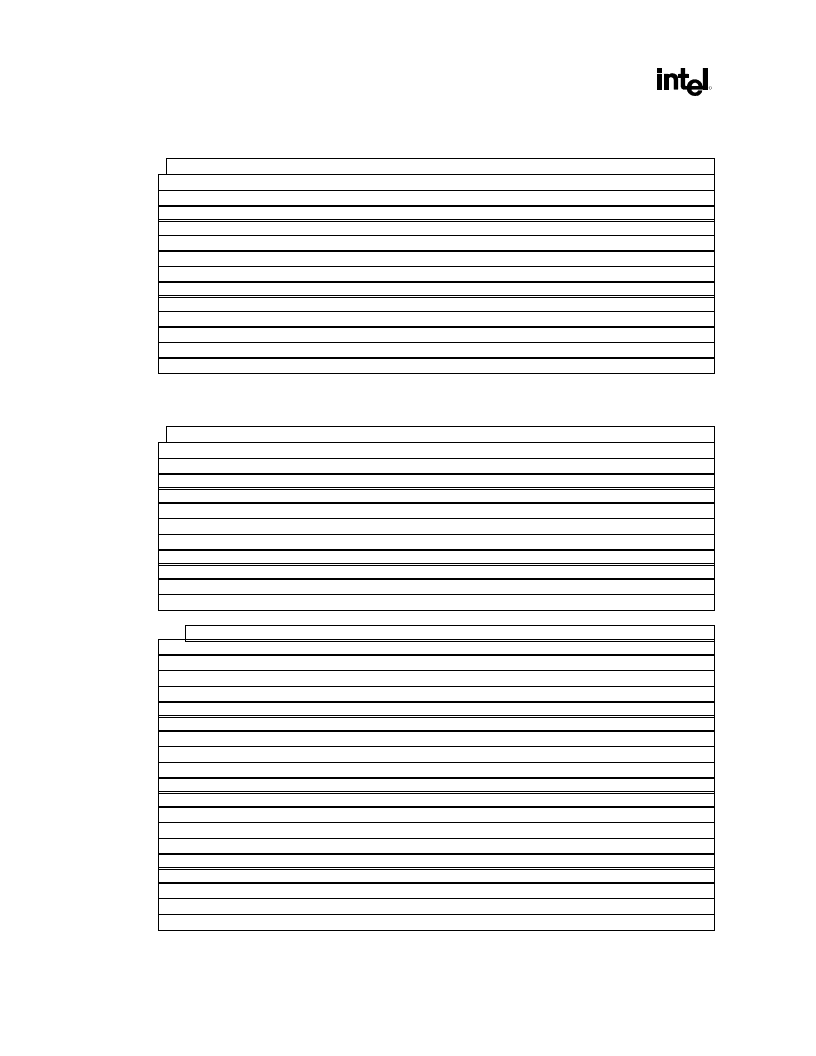

Figures

Figure 1. Intel

815 Chipset Family System Block Diagram ....................................................15

Figure 2. 82815 GMCH Block Diagram....................................................................................16

Figure 3. PAM Registers..........................................................................................................59

Figure 4. System Memory Address Map................................................................................122

Figure 5. Detailed Memory System Address Map..................................................................122

Figure 6. DRAM Array Sockets..............................................................................................139

Figure 7. GMCH Display Cache Interface to 4 MB.................................................................142

Figure 8. 3D/2D Pipeline Preprocessor..................................................................................144

Figure 9. Data Flow for the 3D Pipeline .................................................................................145

Figure 10. GMCH Pinout (Top View-Left Side)......................................................................156

Figure 11. GMCH Pinout (Top View-Right Side)....................................................................157

Figure 12. GMCH BGA Package Dimensions (Top and Side Views)....................................162

Figure 13. GMCH BGA Package Dimensions (Bottom View)................................................163

Figure 14. XOR Tree Implementation....................................................................................165

Tables

Table 1. Supported System Bus and System Memory Bus Frequencies ................................20

Table 2. GMCH PCI Configuration Space (Device 0)..............................................................42

Table 3. Supported System Memory DIMM Configurations.....................................................54

Table 4. Attribute Bit Assignments...........................................................................................58

Table 5. PAM Registers and Associated Memory Segments ..................................................59

Table 6. Summary of GMCH Error Sources, Enables and Status Flags .................................83

Table 7. GMCH Configuration Space (Device 1).....................................................................84

Table 8. Device 2 Configuration Space Address Map (Internal Graphics).............................102

Table 9. Memory Segments and Their Attributes...................................................................123

Table 10. Summay of Transactions Supported By GMCH.....................................................133

Table 11. Host Responses Supported by the GMCH ............................................................134

Table 12. Special Cycles........................................................................................................135

Table 13. Sample Of Possible Mix And Match Options For 4 Row/2 DIMM

Configurations........................................................................................................137

Table 14. Data Bytes on DIMM Used for Programming DRAM Registers.............................138

Table 15. GMCH DRAM Address Mux Function....................................................................139

Table 16. Programmable SDRAM Timing Parameters..........................................................140

Table 17. Memory Size for each configuration :.....................................................................142

Table 18. GMCH Local Memory Address Mapping................................................................143

Table 19. Partial List of Display Modes Supported ................................................................151

Table 20. Partial List of Flat Panel Modes Supported............................................................152

Table 21. Partial List of TV-Out Modes Supported ................................................................153

Table 22. Alphabetical Pin Assignment..................................................................................158

Table 23. Package Dimensions .............................................................................................163

Table 24. XOR Test Pattern Example....................................................................................166

Table 25 XOR Chain 1 35 Inputs Output: SMAA5 (A12)......................................................168

Table 26 XOR Chain 2 33 Inputs Output: SMAA2 (F12) ......................................................168

Table 27 XOR Chain 3 38 Inputs Output: SMAA0 (D13)......................................................169

Table 28 XOR Chain 4 36 Inputs Output: SMAA9 (D13)......................................................169

Table 29 XOR Chain 5 56 Inputs Output: SMD31 (K5) ........................................................170

Table 30 XOR Chain 6 60 Inputs Output: SMAA11 (A13)....................................................171

Table 31 XOR Chain 7 33 Inputs Output: SMAA8 (D12)......................................................171

Table 32 XOR Chain 8 31 Inputs Output: SMAA4 (B12)......................................................172

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| FWA-25A10F | Fuse |

| FWA-30A10F | Fuse |

| FWA-35A21F | Fuse |

| FWA-40A21F | Fuse |

| FWA-45A21F | Fuse |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| FW82815 S L5NQ | 制造商:Intel 功能描述:Graphics and Memory Controller Hub 544-Pin BGA |

| FW82815EM S L4MP | 制造商:Intel 功能描述:GRAPHICS AND MEMORY CONTROLLER HUB (GMCH2-M) |

| FW82815SL5NQ | 制造商:Intel 功能描述: |

| FW828201CA | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Controller Miscellaneous - Datasheet Reference |

| FW82840 S L3TA | 制造商:Intel 功能描述:Memory Controller Hub 544-Pin BGA |

發(fā)布緊急采購,3分鐘左右您將得到回復。