- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370261 > FW82815 Controller Miscellaneous - Datasheet Reference PDF資料下載

參數(shù)資料

| 型號: | FW82815 |

| 英文描述: | Controller Miscellaneous - Datasheet Reference |

| 中文描述: | 控制器雜項-數(shù)據(jù)表參考 |

| 文件頁數(shù): | 67/172頁 |

| 文件大?。?/td> | 795K |

| 代理商: | FW82815 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁當(dāng)前第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁

82815 GMCH

R

Datasheet

67

Bit

Description

15:8

Next Capability Pointer—RO.

This field has two possible values based on APCONT[0] at offset 51h:

A0h when APCONT[0] = 0 (AGP Mode) meaning the next capability pointer is ACAPID.

00h when APCONT[0] = 1 (GFX Mode) meaning that this was the last capability pointer in the list.

7:0

CAP_ID—RO.

This field has the value 1001b to identify the CAP_ID assigned by the PCI SIG for

vendor dependent capability pointers.

3.4.24.

BUFF_SC—System Memory Buffer Strength Control Register

(Device 0)

Address Offset:

92–93h

Default Value:

FFFFh

Access:

Read/Write

Size:

16 bits

This register programs the system memory DRAM interface signal buffer strengths, with the exception of

the CKEs. The programming of these bits should be based on DRAM density (x8 or x16), DRAM

technology (16Mb, 64Mb, 128Mb or 256 Mb), rows populated, etc.. Note that x4 & x32 DRAMs are not

supported. Registered DIMMs and DIMMS with ECC are also not supported and BIOS upon detection

of ECC via SPD, should report to the user that ECC DIMM timings are not supported by the GMCH.

In the descriptions below, the term “Row” is equivalent to one side of one DIMM. In other words, a

“single-sided” DIMM contains one populated row (always an odd numbered), and one empty row (even

numbered). A “double-sided” DIMM contains two populated rows.

All buffer strengths are based on the number of “l(fā)oads” connected to each pin of a given signal group. A

“l(fā)oad” represents one pin of one SDRAM Device. The GMCH pin is implied and not counted in the load

equations. The number of loads on a given signal for a given configuration can be determined entirely

from the width of the SDRAM devices that populate each row in the configuration. This information is

readily available for each row via the Serial Presence Detect mechanism.

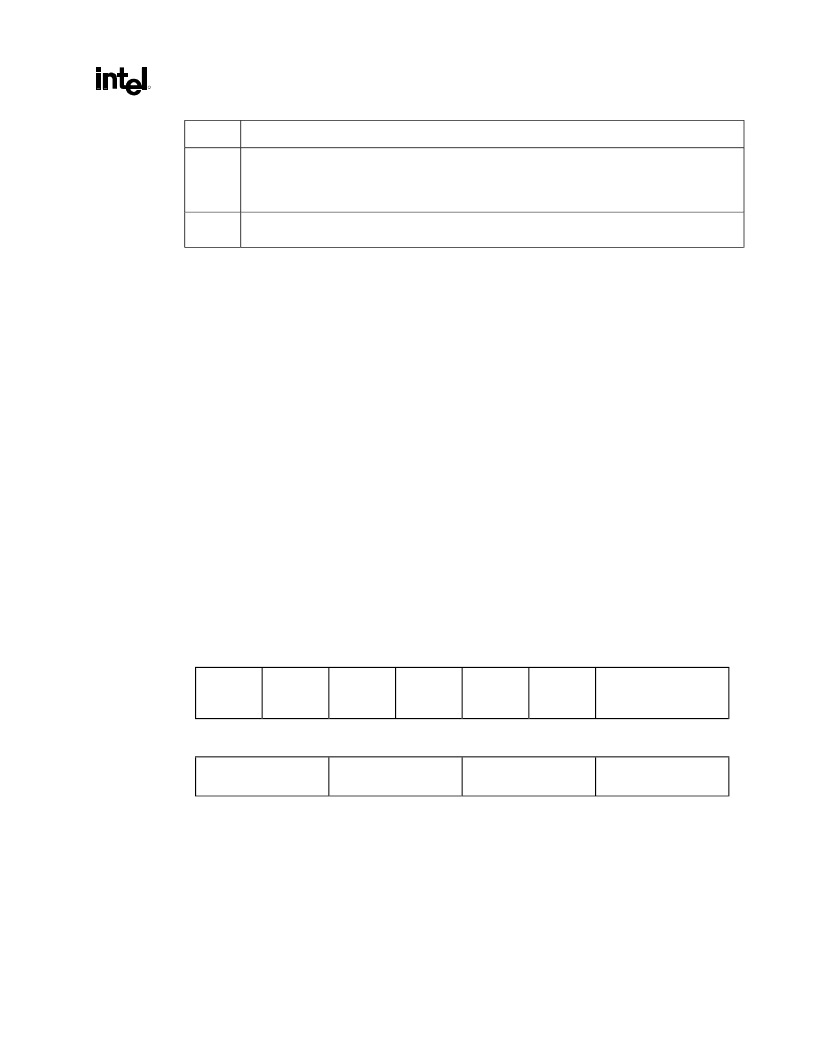

15

14

13

12

11

10

9

8

SCS[5]#

Buffer

Strength

SCS[4]#

Buffer

Strength

SCS[3]#

Buffer

Strength

SCS[2]#

Buffer

Strength

SCS[1]#

Buffer

Strength

SCS[0]#

Buffer

Strength

SMAC[7:4]# Buffer

Strength

7

6

5

4

3

2

1

0

SMAB[7:4]# Buffer

Strength

SMAA[7:4] Buffer

Strength

MD and DQM Buffer

Strengths

Control Buffer Strengths

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| FWA-25A10F | Fuse |

| FWA-30A10F | Fuse |

| FWA-35A21F | Fuse |

| FWA-40A21F | Fuse |

| FWA-45A21F | Fuse |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| FW82815 S L5NQ | 制造商:Intel 功能描述:Graphics and Memory Controller Hub 544-Pin BGA |

| FW82815EM S L4MP | 制造商:Intel 功能描述:GRAPHICS AND MEMORY CONTROLLER HUB (GMCH2-M) |

| FW82815SL5NQ | 制造商:Intel 功能描述: |

| FW828201CA | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Controller Miscellaneous - Datasheet Reference |

| FW82840 S L3TA | 制造商:Intel 功能描述:Memory Controller Hub 544-Pin BGA |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。