- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98069 > S1C88409D 8-BIT, MROM, 8.8 MHz, MICROCONTROLLER, UUC108 PDF資料下載

參數(shù)資料

| 型號(hào): | S1C88409D |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, MROM, 8.8 MHz, MICROCONTROLLER, UUC108 |

| 封裝: | DIE-108 |

| 文件頁(yè)數(shù): | 103/250頁(yè) |

| 文件大小: | 1877K |

| 代理商: | S1C88409D |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)當(dāng)前第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)第158頁(yè)第159頁(yè)第160頁(yè)第161頁(yè)第162頁(yè)第163頁(yè)第164頁(yè)第165頁(yè)第166頁(yè)第167頁(yè)第168頁(yè)第169頁(yè)第170頁(yè)第171頁(yè)第172頁(yè)第173頁(yè)第174頁(yè)第175頁(yè)第176頁(yè)第177頁(yè)第178頁(yè)第179頁(yè)第180頁(yè)第181頁(yè)第182頁(yè)第183頁(yè)第184頁(yè)第185頁(yè)第186頁(yè)第187頁(yè)第188頁(yè)第189頁(yè)第190頁(yè)第191頁(yè)第192頁(yè)第193頁(yè)第194頁(yè)第195頁(yè)第196頁(yè)第197頁(yè)第198頁(yè)第199頁(yè)第200頁(yè)第201頁(yè)第202頁(yè)第203頁(yè)第204頁(yè)第205頁(yè)第206頁(yè)第207頁(yè)第208頁(yè)第209頁(yè)第210頁(yè)第211頁(yè)第212頁(yè)第213頁(yè)第214頁(yè)第215頁(yè)第216頁(yè)第217頁(yè)第218頁(yè)第219頁(yè)第220頁(yè)第221頁(yè)第222頁(yè)第223頁(yè)第224頁(yè)第225頁(yè)第226頁(yè)第227頁(yè)第228頁(yè)第229頁(yè)第230頁(yè)第231頁(yè)第232頁(yè)第233頁(yè)第234頁(yè)第235頁(yè)第236頁(yè)第237頁(yè)第238頁(yè)第239頁(yè)第240頁(yè)第241頁(yè)第242頁(yè)第243頁(yè)第244頁(yè)第245頁(yè)第246頁(yè)第247頁(yè)第248頁(yè)第249頁(yè)第250頁(yè)

S1C88409 TECHNICAL MANUAL

EPSON

181

CHAPTER 5: PERIPHERAL CIRCUITS AND OPERATION (A/D Converter)

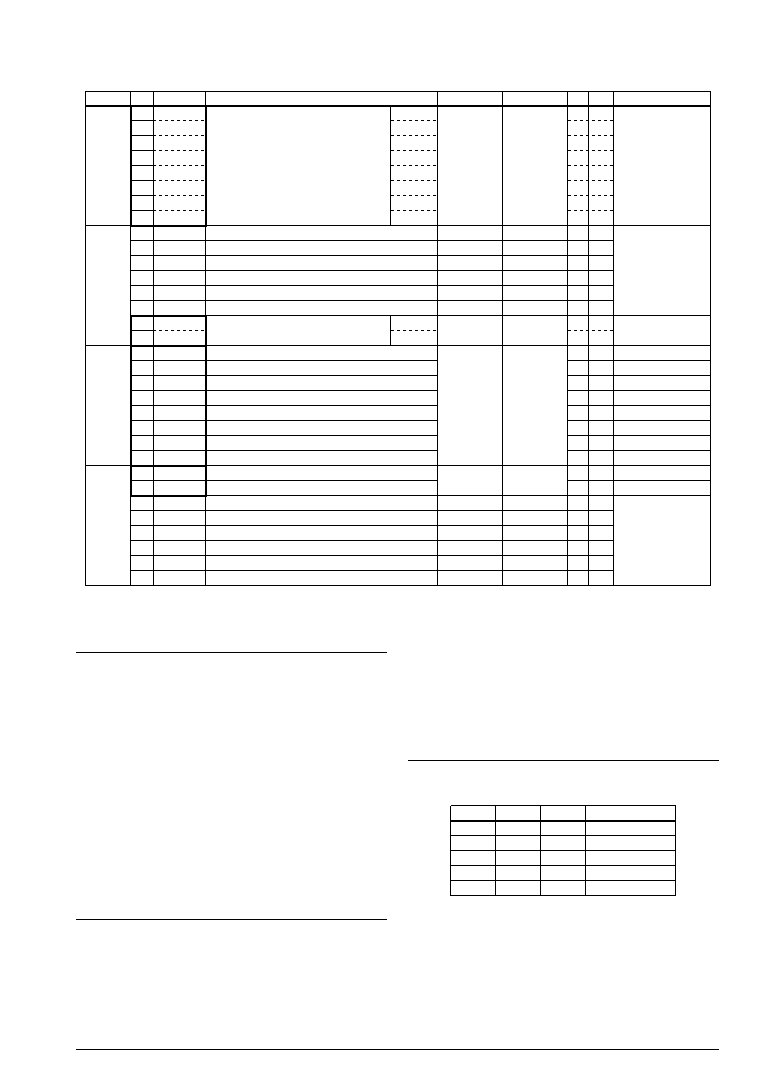

Table 5.18.6.1(b) A/D converter control bits

00FFE8

P37 A/D converter input control

P36 A/D converter input control

P35 A/D converter input control

P34 A/D converter input control

P33 A/D converter input control

P32 A/D converter input control

P31 A/D converter input control

P30 A/D converter input control

R/W

0

I/O port

A/D converter

input

PAD7

PAD6

PAD5

PAD4

PAD3

PAD2

PAD1

PAD0

D7

D6

D5

D4

D3

D2

D1

D0

00FFE9

P37 D/A converter output control

P36 D/A converter output control

–

R/W

–

0

–

I/O port

–

D/A converter

output

–

"0" when being read

PDA7

PDA6

–

D7

D6

D5

D4

D3

D2

D1

D0

00FF81

A/D conversion result

R

–

ADDR9

ADDR8

ADDR7

ADDR6

ADDR5

ADDR4

ADDR3

ADDR2

D7

D6

D5

D4

D3

D2

D1

D0

D9(MSB)

D8

D7

D6

D5

D4

D3

D2

00FF82

–

A/D conversion result

–

R

–

"0" when being read

–

ADDR1

ADDR0

D7

D6

D5

D4

D3

D2

D1

D0

D1

D0(LSB)

Address

Function

R/W

Init

0

1

Comment

Name

Bit

PAD0–PAD7: A/D converter input control

register (00FFE8H)

Sets the P30–P37 terminals as the analog input

terminals for the A/D converter.

When "1" is written: A/D converter input

When "0" is written: I/O port

Reading: Valid

When "1" is written to PADn, the P3n terminal is

set to the analog input terminal ADn. (n=0–7)

When "0" is written, the terminal is used with the

I/O port.

At initial reset, the PAD register is set to "0" (I/O

port).

PDA6, PDA7: D/A converter output control

register (00FFE9HD6, D7)

The PDA6 and PDA7 registers set the P36 and P37

terminals to the analog output terminal of the D/A

converter, respectively. Those register settings

have priority over the PAD6 and PAD7 settings.

Therefore, when using the P36 terminal (P37

terminal) as the analog input for the A/D con-

verter, fix the PDA6 (PDA7) register at "0".

At initial reset, the PDA register is set to "0" (I/O

port).

PSAD0–PSAD2: A/D converter division ratio

selection register (00FF13HD0–D2)

Selects the clock for the A/D converter.

Table 5.18.6.2 Input clock selection

Division ratio

fOSC3/16

fOSC3/8

fOSC3/4

fOSC3/2

fOSC3/1

PSAD2

1

0

PSAD1

×

1

0

PSAD0

×

1

0

1

0

This setting controls the division ratio of the

prescaler.

At initial reset, the PSAD register is set to "0"

(fOSC3/1).

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| S1C88816D | 8-BIT, MROM, 8.2 MHz, MICROCONTROLLER, UUC164 |

| S1C88832F0A0100 | MICROCONTROLLER, PQFP128 |

| S1C88848D0A0100 | 8-BIT, MROM, 8.2 MHz, MICROCONTROLLER, UUC192 |

| S1C8F360F | 8-BIT, FLASH, 8.2 MHz, MICROCONTROLLER, PQFP176 |

| S1D13305F00B | 640 X 256 PIXELS CRT CHAR OR GRPH DSPL CTLR, PQFP60 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| S1C88649 | 制造商:EPSON 制造商全稱:EPSON 功能描述:8-bit Single Chip Microcomputer |

| S1C88650 | 制造商:EPSON 制造商全稱:EPSON 功能描述:8-bit Single Chip Microcomputer |

| S1C88655 | 制造商:EPSON 制造商全稱:EPSON 功能描述:8-bit Single Chip Microcomputer |

| S1C88816 | 制造商:EPSON 制造商全稱:EPSON 功能描述:8-bit Single Chip Microcomputer |

| S1C88848 | 制造商:EPSON 制造商全稱:EPSON 功能描述:8-bit Single Chip Microcomputer |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。