- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄67681 > IBM21P100BGC PCI BUS CONTROLLER, PBGA304 PDF資料下載

參數(shù)資料

| 型號: | IBM21P100BGC |

| 元件分類: | 總線控制器 |

| 英文描述: | PCI BUS CONTROLLER, PBGA304 |

| 封裝: | 31 X 31 MM, PLASTIC, BGA-304 |

| 文件頁數(shù): | 85/144頁 |

| 文件大小: | 5197K |

| 代理商: | IBM21P100BGC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁當(dāng)前第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁

IBM21P100BGC

IBM 133 PCI-X Bridge R2.0

ppb20_pcix_regs.fm.01

October 15, 2001

Configuration Registers

Page 45 of 144

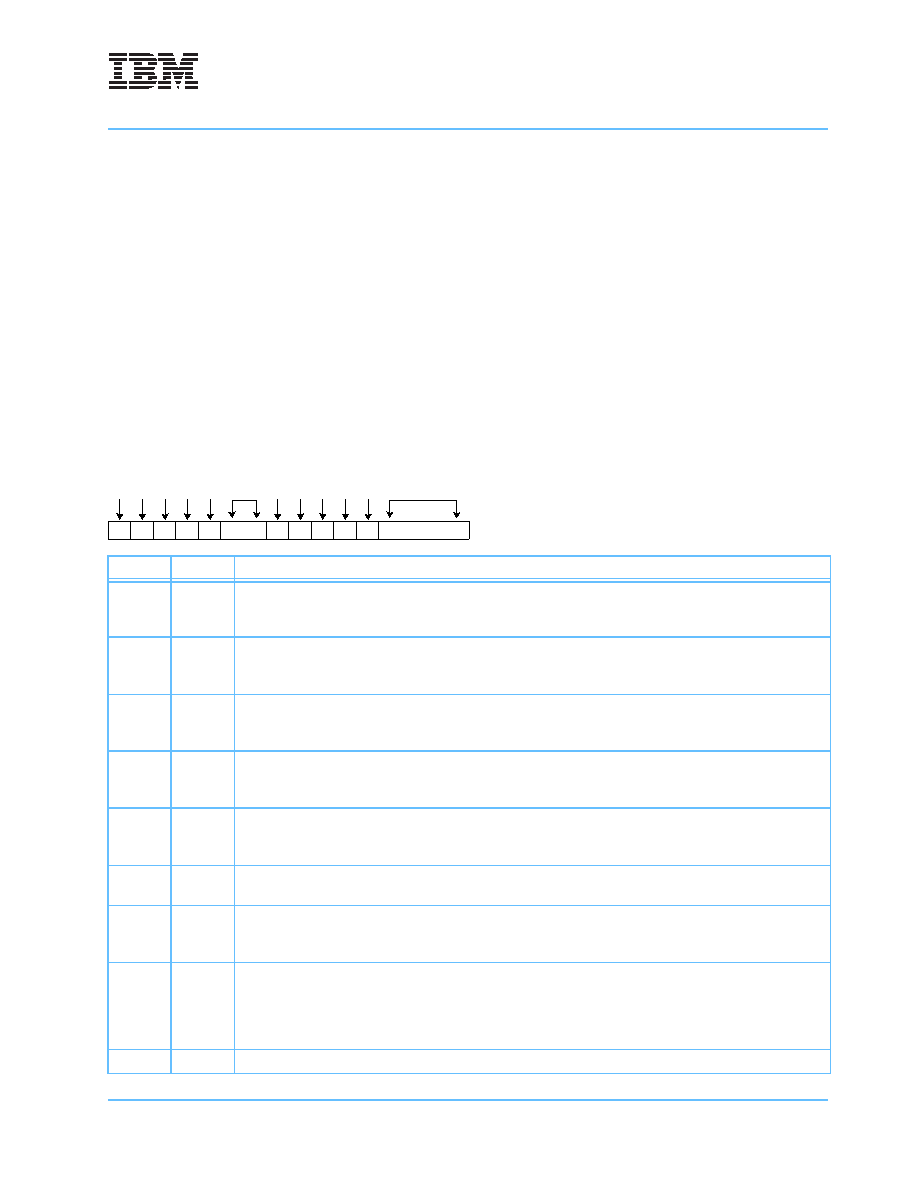

5.2.4.4 Status Register

This register records the status of PCI events.

Address Offset

x‘06’

Access

See individual bit fields. Reads to this register behave normally. Writes are

slightly different in that bits can be reset, but not set. A bit is reset whenever the

register is written, and the data in the corresponding bit location is a ‘1’.

Reset Value

x‘02B0’ in the PCI mode, x‘0230’ in the PCI-X mode

De

te

c

te

d

Pa

ri

ty

Erro

r

S

ign

al

ed

S

y

st

em

E

rr

o

r

R

e

ce

iv

ed

Ma

st

er

A

b

o

rt

R

e

ce

iv

ed

T

a

rg

et

A

b

or

t

S

ign

al

ed

T

a

rg

et

A

b

o

rt

D

e

vi

ce

S

e

le

ct

T

imi

n

g

M

a

s

te

r

Da

ta

P

a

ri

ty

Erro

r

Fa

s

t

Ba

c

k

-to

-Ba

c

k

C

a

p

a

b

le

Re

s

e

rv

e

d

66

M

H

z

C

ap

ab

le

C

a

pa

bi

lit

ie

s

Li

st

Re

s

e

rv

e

d

15 14 13 12 11 10

9

8

7

6

5

4

3

2

1

0

Bit(s)

Access

Field Name and Description

15

RW

Detected Parity Error Status

0

Device did not detect a parity error.

1

Device detected a parity error.

14

RW

Signaled System Error Status

0

Device did not generate a SERR# signal.

1

Device generated a SERR# signal.

13

RW

Received Master Abort Status

0

Bus master transaction was not terminated with a bus master abort.

1

Bus master transaction terminated with bus master abort.

12

RW

Received Target Abort Status

0

Bus master transaction was not terminated by a target abort.

1

Bus master transaction terminated by a target abort.

11

RW

Signaled Target Abort Status

0

Target device did not terminate a transaction with a target abort.

1

Target device terminated a transaction with a target abort.

10:9

RO

Device Select (DEVSEL) Timing Status

01

Medium.

8

RW

Data Parity Status

0

No data parity errors encountered.

1

Data parity errors encountered (this bit for bus masters only).

7

RO

Fast Back-to-Back Status

0

Target not capable of accepting fast back-to-back transactions in the PCI-X mode.

1

Target capable of accepting fast back-to-back transactions in the conventional PCI mode.

This bit is set by hardware when the primary interface is in the PCI mode and is set to a b‘0’ when the primary

interface is in the PCI-X mode.

6

RO

Reserved

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IBM25403GCX-3JC76C2 | RISC PROCESSOR, PQFP16 |

| IBM25405GP-3BA200C2 | RISC PROCESSOR, PBGA456 |

| IBM25EMPPC603EFG-100 | 32-BIT, 100 MHz, RISC PROCESSOR, PQFP240 |

| IBM25EMPPC603EBG-100 | 32-BIT, 100 MHz, RISC PROCESSOR, CBGA255 |

| IBM25EMPPC740LDBC4000 | 32-BIT, 400 MHz, RISC PROCESSOR, CBGA255 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IBM24L5086 | 制造商:AVED MEMORY PRODUCTS 功能描述: 制造商:AVED Memory Products 功能描述: |

| IBM25403GCX-3BC80C2 | 制造商:IBM 功能描述:RISC PROCESSOR, 160 Pin Plastic BGA |

| IBM25403GCX-3JC50C2 | 制造商:IBM 功能描述:403GCX-3JC50C2 |

| IBM25403GCX-3JC66C2 | 制造商:IBM 功能描述: |

| IBM25403GCX3JC76C2 | 制造商:IBM 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。