- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄67681 > IBM21P100BGC PCI BUS CONTROLLER, PBGA304 PDF資料下載

參數(shù)資料

| 型號: | IBM21P100BGC |

| 元件分類: | 總線控制器 |

| 英文描述: | PCI BUS CONTROLLER, PBGA304 |

| 封裝: | 31 X 31 MM, PLASTIC, BGA-304 |

| 文件頁數(shù): | 16/144頁 |

| 文件大小: | 5197K |

| 代理商: | IBM21P100BGC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁當前第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁

IBM21P100BGC

IBM 133 PCI-X Bridge R2.0

Signal Descriptions

Page 112 of 144

ppb20_signals.fm.01

October 15, 2001

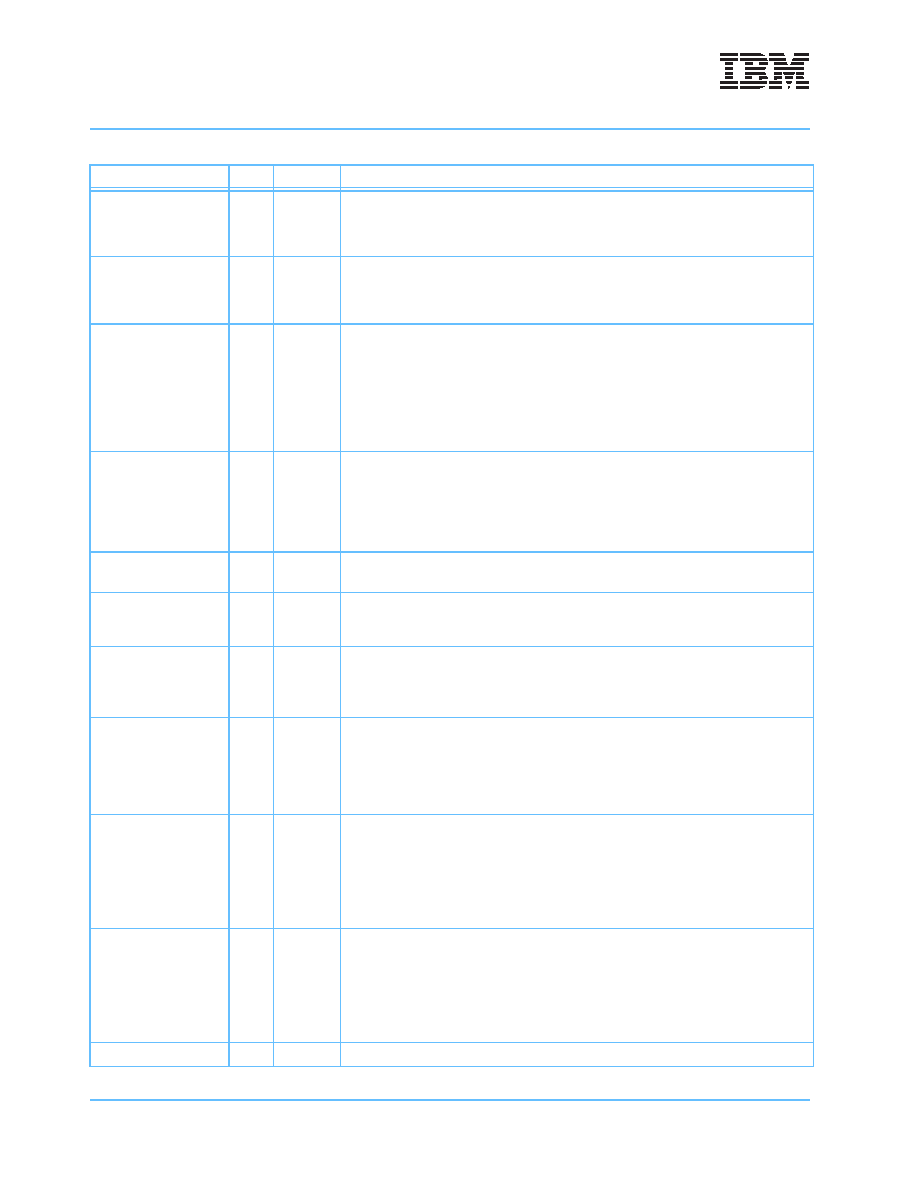

S_PAR

I/O

1

Parity

Parity protection bit for the lower half of the address/data and command/byte enable

buses on the secondary interface. It provides even parity across S_AD(31:00) and

S_C/BE(3:0)#.

S_PAR64

I/O

1

Parity Upper DWord

Parity protection bit for the upper half of the address/data and command/byte enable

buses on the secondary interface. It provides even parity across S_AD(63:32) and

S_C/BE(7:4)#.

S_PERR#

I/O

1

Parity Error

Used to report data parity errors on the secondary interface.

S_PERR# is monitored by the bridge when performing a secondary bus write transaction

on behalf of a primary bus master or when serving as the selected slave for a secondary

bus read transaction.

S_PERR# is driven by the bridge when performing a secondary bus read transaction on

behalf of a primary bus master or when serving as the selected slave during a secondary

bus write transaction.

S_REQ1GNT#

I

1

Request 1

This is a dual-purpose signal:

When the bridge’s internal arbiter is enabled, this signal is used as a request input, to be

activated by a secondary bus master requesting the use of the secondary bus.

When the internal arbiter is disabled, this signal is used by the bridge as its grant input

signal.

S_REQ2# - S_REQ6#

I

5

Requests 2-6

Activated by the secondary bus masters to request the use of the secondary bus.

S_REQ64#

I/O

1

Request 64-Bit Transfer

This signal, when asserted by the current master on the secondary bus, indicates a

desire to transfer data using 64 bits.

S_RST#

O

1

Secondary Bus Reset

S_RST#, driven by the bridge, is the secondary bus reset signal.

Asserted when P_RST# is active or when the secondary bus reset bit in the bridge con-

trol register is set.

S_SERR#

I

1

System Error

Used to report address parity errors and other system errors where the results will be

catastrophic.

S_SERR# is monitored by the bridge to detect these errors on the secondary bus. When

S_SERR# is asserted, it results in P_SERR# being asserted on the primary bus by the

bridge.

S_STOP#

I/O

1

Stop

Indicates that the current target is requesting that the initiator stop the current transac-

tion on the secondary bus.

S_STOP# is monitored by the bridge when performing a secondary bus transaction on

behalf of a primary pus master.

S_STOP# is driven by the bridge when addressed as a target and is asserted low to indi-

cate target termination.

S_TRDY#

I/O

1

Target Ready

Indicates the ability of the target on the secondary bus to complete the current data

phase of the transaction. It is used in conjunction with the S_IRDY# signal.

S_TRDY# is monitored by the bridge when performing a secondary bus transaction on

behalf of a primary bus master.

S_TRDY# is driven by the bridge when a secondary bus master is performing a transac-

tion in which the bridge is the selected target.

Total

98

Table 7-2. Secondary Interface Signal List (Page2of 2)

Signal Name

I/O

Width

Description

相關PDF資料 |

PDF描述 |

|---|---|

| IBM25403GCX-3JC76C2 | RISC PROCESSOR, PQFP16 |

| IBM25405GP-3BA200C2 | RISC PROCESSOR, PBGA456 |

| IBM25EMPPC603EFG-100 | 32-BIT, 100 MHz, RISC PROCESSOR, PQFP240 |

| IBM25EMPPC603EBG-100 | 32-BIT, 100 MHz, RISC PROCESSOR, CBGA255 |

| IBM25EMPPC740LDBC4000 | 32-BIT, 400 MHz, RISC PROCESSOR, CBGA255 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| IBM24L5086 | 制造商:AVED MEMORY PRODUCTS 功能描述: 制造商:AVED Memory Products 功能描述: |

| IBM25403GCX-3BC80C2 | 制造商:IBM 功能描述:RISC PROCESSOR, 160 Pin Plastic BGA |

| IBM25403GCX-3JC50C2 | 制造商:IBM 功能描述:403GCX-3JC50C2 |

| IBM25403GCX-3JC66C2 | 制造商:IBM 功能描述: |

| IBM25403GCX3JC76C2 | 制造商:IBM 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復。