- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄67681 > IBM21P100BGC PCI BUS CONTROLLER, PBGA304 PDF資料下載

參數(shù)資料

| 型號: | IBM21P100BGC |

| 元件分類: | 總線控制器 |

| 英文描述: | PCI BUS CONTROLLER, PBGA304 |

| 封裝: | 31 X 31 MM, PLASTIC, BGA-304 |

| 文件頁數(shù): | 12/144頁 |

| 文件大小: | 5197K |

| 代理商: | IBM21P100BGC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁當(dāng)前第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁

IBM21P100BGC

IBM 133 PCI-X Bridge R2.0

ppb20_signals.fm.01

October 15, 2001

Signal Descriptions

Page 109 of 144

7. Signal Descriptions

This section describes in detail each input and output signal of the IBM 133 PCI-X Bridge R2.0. Throughout

this section, trailing pound signs, for example P_ACK64#, designate signals that are active low.

7.1 Primary Interface Signals

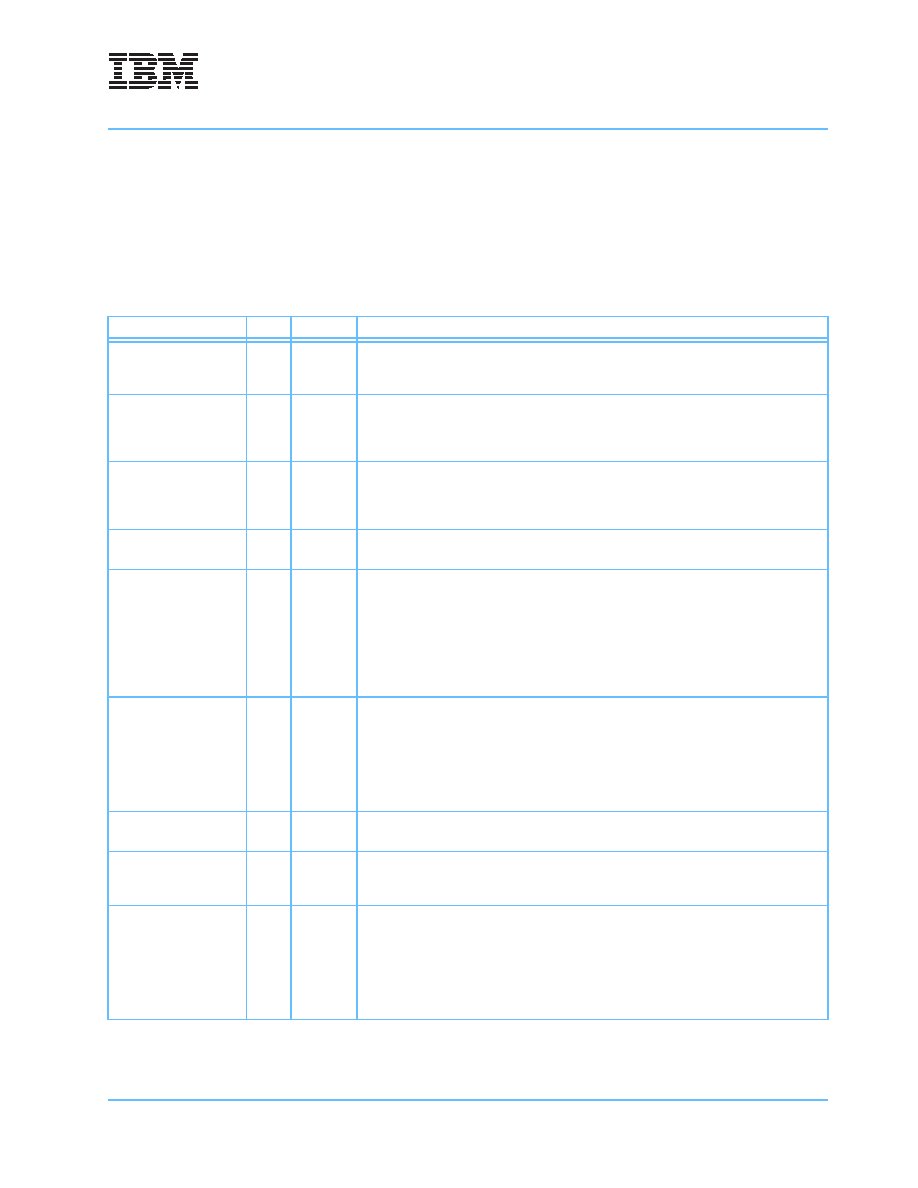

Table 7-1. Primary Interface Signal List (Page1of 2)

Signal Name

I/O

Width

Description

P_ACK64#

I/O

1

Acknowledge 64-Bit Transfer

Asserted by the currently addressed target on the primary bus to indicate its willingness

to transfer data using 64 bits.

P_AD(63:00)

I/O

64

Multiplexed Address and Data

64-bit multiplexed address and data bus, shared by other devices on the primary bus.

During a transaction, this bus contains the physical bus address, attributes, or data, or it

may be reserved.

P_C/BE(7:0)#

I/O

8

Multiplexed Bus Command and Byte Enables

During a transaction, these eight bits define the bus command, attributes, or byte

enables for the transfer. These signals are shared with other agents on the primary bus

and at times may be reserved.

P_CLK

I

1

Clock

Received by the bridge and provides timing for all operations on the primary interface.

P_DEVSEL#

I/O

1

Device Select

Asserted by the target on the primary bus that decoded the address of the current trans-

action as being within one of its address ranges.

P_DEVSEL# is monitored by the bridge when performing a primary bus transaction on

behalf of a secondary bus master.

P_DEVSEL# is driven by the bridge when a primary bus master is performing a transac-

tion on the primary bus intended for a secondary bus slave or the bridge's configuration

registers.

P_FRAME#

I/O

1

Cycle Frame

Defines the beginning and duration of each primary bus transaction and is controlled by

the initiator of the operation.

P_FRAME# is driven by the bridge when performing a primary bus transaction on behalf

of a secondary bus master.

P_FRAME# is monitored by the bridge when a primary bus master is performing a trans-

action on the primary bus.

P_GNT#

I

1

Grant

Indicates that the bridge has been granted access to the primary bus.

P_IDSEL

I

1

Initialization Device Select

Used as a chip select during configuration read and write transactions on the primary

bus.

P_IRDY#

I/O

1

Initiator Ready

Indicates the ability of the initiator on the primary bus to complete the current data phase

of the transaction. It is used in conjunction with P_TRDY#.

P_IRDY# is driven by the bridge when performing a primary bus transaction on behalf of

a secondary bus master.

P_IRDY# is monitored by the bridge when a primary bus master is performing a transac-

tion on the primary bus to or through the bridge.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IBM25403GCX-3JC76C2 | RISC PROCESSOR, PQFP16 |

| IBM25405GP-3BA200C2 | RISC PROCESSOR, PBGA456 |

| IBM25EMPPC603EFG-100 | 32-BIT, 100 MHz, RISC PROCESSOR, PQFP240 |

| IBM25EMPPC603EBG-100 | 32-BIT, 100 MHz, RISC PROCESSOR, CBGA255 |

| IBM25EMPPC740LDBC4000 | 32-BIT, 400 MHz, RISC PROCESSOR, CBGA255 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IBM24L5086 | 制造商:AVED MEMORY PRODUCTS 功能描述: 制造商:AVED Memory Products 功能描述: |

| IBM25403GCX-3BC80C2 | 制造商:IBM 功能描述:RISC PROCESSOR, 160 Pin Plastic BGA |

| IBM25403GCX-3JC50C2 | 制造商:IBM 功能描述:403GCX-3JC50C2 |

| IBM25403GCX-3JC66C2 | 制造商:IBM 功能描述: |

| IBM25403GCX3JC76C2 | 制造商:IBM 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。