- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379500 > UPD488448FB-C80-45-DQ1 (NEC Corp.) 128 M-bit Direct Rambus⑩ DRAM PDF資料下載

參數(shù)資料

| 型號: | UPD488448FB-C80-45-DQ1 |

| 廠商: | NEC Corp. |

| 英文描述: | 128 M-bit Direct Rambus⑩ DRAM |

| 中文描述: | 128 M位DRAM的直接Rambus的⑩ |

| 文件頁數(shù): | 59/80頁 |

| 文件大?。?/td> | 1902K |

| 代理商: | UPD488448FB-C80-45-DQ1 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁當(dāng)前第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁

Data Sheet M14837EJ3V0DS00

59

μ

PD488448 for Rev. P

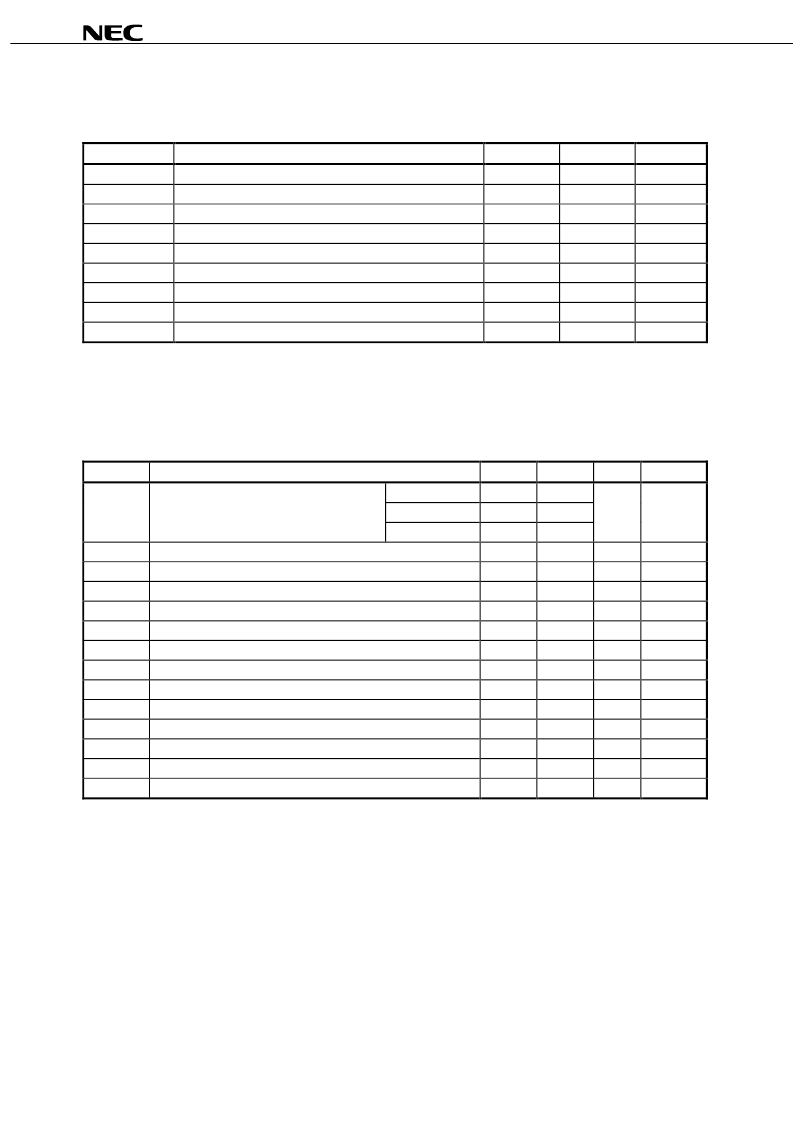

28. Electrical Characteristics

Electrical Characteristics

Symbol

Parameter and Conditions

MIN.

MAX.

Unit

Θ

JC

Junction-to-Case thermal resistance

—

0.5

°

C/Watt

I

REF

V

REF

current

@

V

REF,MAX

–10

+10

μA

I

OH

RSL output high current

@

(0

≤

V

OUT

≤

V

DD

)

–10

+10

μA

I

ALL

RSL I

OL

current

@

V

OL

=0.9 V, V

DD,MIN

, T

j,MAX

Note

30

90

mA

I

OL

RSL I

OL

current resolution step

—

2.0

mA

r

OUT

Dynamic output impedance

150

—

I

I,CMOS

CMOS input leakage current

@

(0

≤

V

I,CMOS

≤

V

CMOS

)

–10.0

+10.0

μA

V

OL,CMOS

CMOS output low voltage

@

I

OL,CMOS

= 1.0 mA

—

0.3

V

V

OH,CMOS

CMOS output high voltage

@

I

OH,CMOS

=

–

0.25 mA

V

CMOS

–

0.3

—

V

Note

This measurement is made in manual current control mode; i.e. with all output device legs sinking current.

29. Timing Characteristics

Timing Characteristics

Symbol

Parameter

MIN.

MAX.

Unit

Figure(s)

t

Q

CTM-to-DQA/DQB output time

t

CYCLE

= 2.50 ns

–0.260

Note3

+0.260

Note3

ns

Figure 32-1

t

CYCLE

= 2.81 ns

–0.300

Note2,3

+0.300

Note2,3

t

CYCLE

= 3.33 ns

–0.350

Note1,3

+0.350

Note1,3

t

QR

, t

QF

DQA/DQB output rise and fall times

0.2

0.45

ns

Figure 32-1

t

Q1

SCK-to-SIO0

delay

@

C

LOAD,MAX

= 20 pF (SD read packet)

—

10

ns

Figure 34-1

t

HR

SCK(pos)-to-SIO0 delay @ C

LOAD,MAX

= 20pF (SD read data hold)

2

—

ns

Figure 34-1

t

QR1

, t

QF1

SIO

OUT

rise/fall

@

C

LOAD,MAX

=

20 pF

—

5

ns

Figure 34-1

t

PROP1

SIO0-to-SIO1 or SIO1-to-SIO0

delay

@

C

LOAD,MAX

=

20 pF

—

10

ns

Figure 34-1

t

NAPXA

NAP exit delay - phase A

—

50

ns

Figure 23-4

t

NAPXB

NAP exit delay - phase B

—

40

ns

Figure 23-4

t

PDNXA

PDN exit delay - phase A

—

4

μ

s

Figure 23-4

t

PDNXB

PDN exit delay - phase B

—

9,000

t

CYCLE

Figure 23-4

t

AS

ATTN-to-STBY power state delay

—

1

t

CYCLE

Figure 23-2

t

SA

STBY-to-ATTN power state delay

—

0

t

CYCLE

Figure 23-2

t

ASN

ATTN/STBY-to-NAP power state delay

—

8

t

CYCLE

Figure 23-3

t

ASP

ATTN/STBY-to-PDN power state delay

—

8

t

CYCLE

Figure 23-3

Notes 1

. This parameter also applies to a -C80 or -C71 part when operated with t

CYCLE

=3.33 ns.

2.

This parameter also applies to a -C80 part when operated with t

CYCLE

=2.81 ns.

3.

t

Q,MIN

and t

Q,MAX

for other t

CYCLE

values can be interpolated between or extrapolated from the timings at the

3 specified t

CYCLE

values.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| UPD488448FB-C80-45-DQ2 | 128 M-bit Direct Rambus⑩ DRAM |

| UPD488448FB-C71-45-DQ1 | 128 M-bit Direct Rambus⑩ DRAM |

| UPD488448FB-C71-45-DQ2 | 128 M-bit Direct Rambus⑩ DRAM |

| UPD488448FB-C60-53-DQ2 | 128 M-bit Direct Rambus⑩ DRAM |

| UPD488448FF-C80-45-DQ1 | 128 M-bit Direct Rambus⑩ DRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| UPD4990AG-A | 制造商:Renesas Electronics 功能描述:Cut Tape |

| UPD4991ACX-A | 制造商:Renesas Electronics Corporation 功能描述: |

| UPD4992CX-A | 制造商:Renesas Electronics 功能描述:Cut Tape |

| UPD50256CP15 | 制造商:HIT 功能描述:50256 HITACHI'86 SMT N9F8A |

| UPD50256CP-15 | 制造商:HIT 功能描述:50256 HITACHI'86 SMT N9F8A |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。