- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄298813 > AD6652XBC (ANALOG DEVICES INC) SPECIALTY TELECOM CIRCUIT, PBGA256 PDF資料下載

參數(shù)資料

| 型號(hào): | AD6652XBC |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 通信及網(wǎng)絡(luò) |

| 英文描述: | SPECIALTY TELECOM CIRCUIT, PBGA256 |

| 封裝: | 17 X 17 MM, MINI, BGA-256 |

| 文件頁(yè)數(shù): | 63/76頁(yè) |

| 文件大?。?/td> | 1802K |

| 代理商: | AD6652XBC |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)當(dāng)前第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)

AD6652

Preliminary Technical Data

Rev. PrC | Page 66 of 76

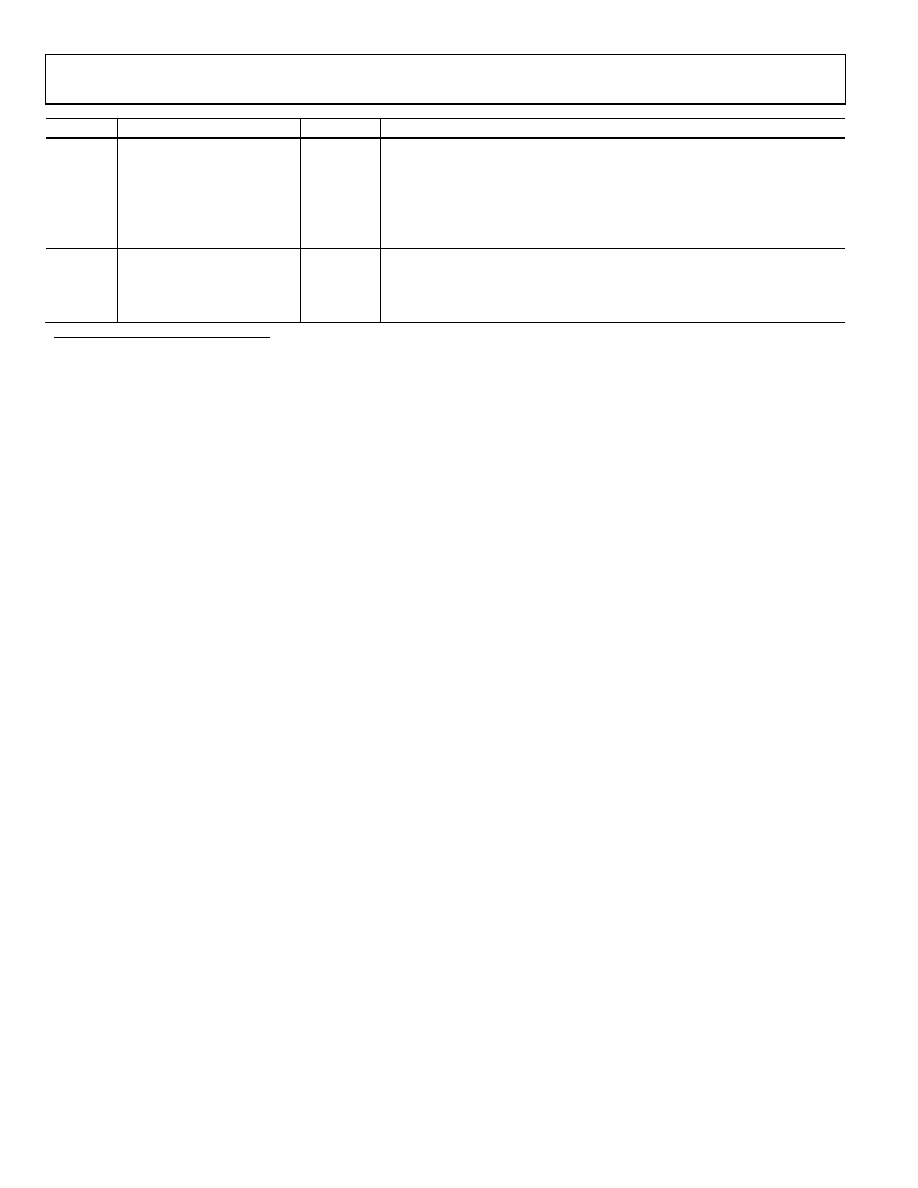

Comments

Address

Register

Bit Width

1:

Channel data interleaved

1:

2-channel mode/separate AB

0:

de/AB same port

4-channel mo

0:

AGC_CH select

1:

Data comes from AGCs

0:

Data comes from channels

1E

Port Clock Control

3

2–1:

PCLK divisor

0:

PCLK master/slave2

0:

Slave

1:

Master

1 Set the LHB A and/or LHB B enable bits to logic low only when the entire block (interleav

ed

s

f

op each time the AGC is initialized.

scale used for the CIC filter and

e CIC decimating filter. This number can be

set between 1 and 4 with 00 meaning one sample and 11

meaning four samples.

0x11: AGC A Update Decimation

This 12-bit register sets the AGC decimation ratio from 1 to

4096. Set an appropriate scaling factor to avoid loss of bits.

0x12: AGC B Control Register

Bits 7–5 define the output word length of the AGC. The output

word can be 4 to 8, 10, 12, or 16 bits wide. The control register

bit representation to obtain different output word lengths is

given in Table 29.

Bit 4 of this register sets the mode of operation for the AGC.

When this bit is 0, the AGC tracks to maintain the output signal

level; when this bit is 1, the AGC tracks to maintain a constant

clipping error. See the Automatic Gain Control section for more

details about these two modes.

Bits 3–1 are used to configure the synchronization of the AGC.

The CIC decimator filter in the AGC can be indirectly

erated signal. When synchro-

e

e hold-off counter of AGC B shares the pin sync

assigned to DDC processing Channel 2. Therefore, if you intend

d value is updated. Writing a logic

ation

.

s;

on

are

s, an

utput from the CIC filter and the

ds the next output sample

lly.

ynchronizes the AGC. If this

bit is set, only the first sync high is recognized and succeeding

sync events are ignored until Bit 1 is reset.

e LB< and AGC functions) is to be shut down.

2 PCLK boots as a slave.

0x0E: AGC A Loop Gain

This 8-bit register defines the open loop gain K. Its value can be

set from 0 to 0.996 in steps of 0.0039. This value of K is updat

in the AGC loop each time the AGC is initialized.

0x0F: AGC A Pole Location

This 8-bit register defines the open loop filter pole location P. It

value can be set from 0 to 0.996 in steps of 0.0039. This value o

P is updated in the AGC lo

This open loop pole location directly impacts the closed loop

pole locations. See the Automatic Gain Control section.

0x10: AGC A Average Samples

This 6-bit register contains the

the number of power samples to be averaged before being fed to

the CIC filter.

Bits 5–2 define the scale used for the CIC filter.

Bits 1–0 define the number of samples to be averaged before

they are sent to th

synchronized to an externally gen

nized, the AGC outputs an update sample for the AGC error

calculation and filtering. This way, the AGC gain changes can b

synchronized to a Rake receiver or other external block.

Note: Th

to use the AGC B’s hold-off counter, you must attach the

external sync signal to the pin sync that will be assigned to

DDC Channel 2. The hold-off counter must be programmed

with a 16-bit number that corresponds to the desired delay

before a new CIC decimate

high to the proper pin sync pin triggers the AGC hold-off

counter with a retriggerable one-shot pulse every time the pin is

written high.

Bit 3 is the sync now bit. If you choose not to use pin sync

signals, you may use the Sync Now command by programming

this bit high. This performs an immediate start of decim

for a new update sample and initializes the AGC, if Bit 2 is set.

This bit has a one-shot characteristic and does not need to be

reset in order to respond to a new logic high being written to it

Use of the sync now bit bypasses the AGC hold-off counter

therefore, the name Sync Now.

Bit 2 is used to determine whether the AGC should initialize

a Sync Now or not. When this bit is set, the CIC filter is cleared

and new values for CIC decimation, number of averaging

samples, CIC scale, signal gain Gs, gain K, and pole parameter P

are loaded. When Bit 2 = 0, the above-mentioned parameters

not updated and the CIC filter is not cleared. In both case

AGC update sample is o

decimator starts operating towar

whenever a Sync Now occurs.

Bit 1 is used to ignore repetitive Pin_Sync signals. In some

applications, the synchronization signal may occur periodica

If this bit is clear, each Pin_Sync res

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD7575JP-REEL | 1-CH 8-BIT SUCCESSIVE APPROXIMATION ADC, PARALLEL ACCESS, PQCC20 |

| AD7575KP-REEL | 1-CH 8-BIT SUCCESSIVE APPROXIMATION ADC, PARALLEL ACCESS, PQCC20 |

| AD7741YR-REEL7 | VOLTAGE-FREQUENCY CONVERTER, 6.144 MHz, PDSO8 |

| AD8402AR1-REEL | DUAL 1K DIGITAL POTENTIOMETER, 3-WIRE SERIAL CONTROL INTERFACE, 256 POSITIONS, PDSO14 |

| AD8402ARU100-REEL | DUAL 100K DIGITAL POTENTIOMETER, 3-WIRE SERIAL CONTROL INTERFACE, 256 POSITIONS, PDSO14 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD6653 | 制造商:AD 制造商全稱:Analog Devices 功能描述:IF Diversity Receiver |

| AD6653-125EBZ | 制造商:Analog Devices 功能描述:Evaluation Board For AD6653 制造商:Analog Devices 功能描述:EVAL BD FOR AD6653 - Bulk 制造商:Analog Devices 功能描述:KIT EVALUATION BOARD AD6653 |

| AD6653-150EBZ | 制造商:Analog Devices 功能描述:EVAL BD FOR AD6653 - Bulk |

| AD6653BCPZ-125 | 制造商:Analog Devices 功能描述:IF DIVERSITY RCVR 64LFCSP EP - Trays 制造商:Rochester Electronics LLC 功能描述: 制造商:Analog Devices 功能描述:IC RECEIVER IF DIVERSITY LFCSP64 |

| AD6653BCPZ-150 | 制造商:Analog Devices 功能描述:IF DIVERSITY RCVR 64LFCSP EP - Trays 制造商:Analog Devices 功能描述:IC RECEIVER IF DIVERSITY LFCSP64 制造商:Analog Devices 功能描述:IC, RECEIVER, IF DIVERSITY, LFCSP64 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。