- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄298813 > AD6652XBC (ANALOG DEVICES INC) SPECIALTY TELECOM CIRCUIT, PBGA256 PDF資料下載

參數(shù)資料

| 型號(hào): | AD6652XBC |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 通信及網(wǎng)絡(luò) |

| 英文描述: | SPECIALTY TELECOM CIRCUIT, PBGA256 |

| 封裝: | 17 X 17 MM, MINI, BGA-256 |

| 文件頁(yè)數(shù): | 28/76頁(yè) |

| 文件大?。?/td> | 1802K |

| 代理商: | AD6652XBC |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)當(dāng)前第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)

AD6652

Preliminary Technical Data

Rev. PrC | Page 34 of 76

RCIC2 OUTPUT LEVEL

After the proper scaling factor has been determined, the output

level from the rCIC2 stage can be determined using the

following equation:

()

level

input

L

M

OL

rCIC

S

rCIC

_

2

×

=

where:

input_level is normally full scale (or 1) from the ADC to the

rCIC2 stage.

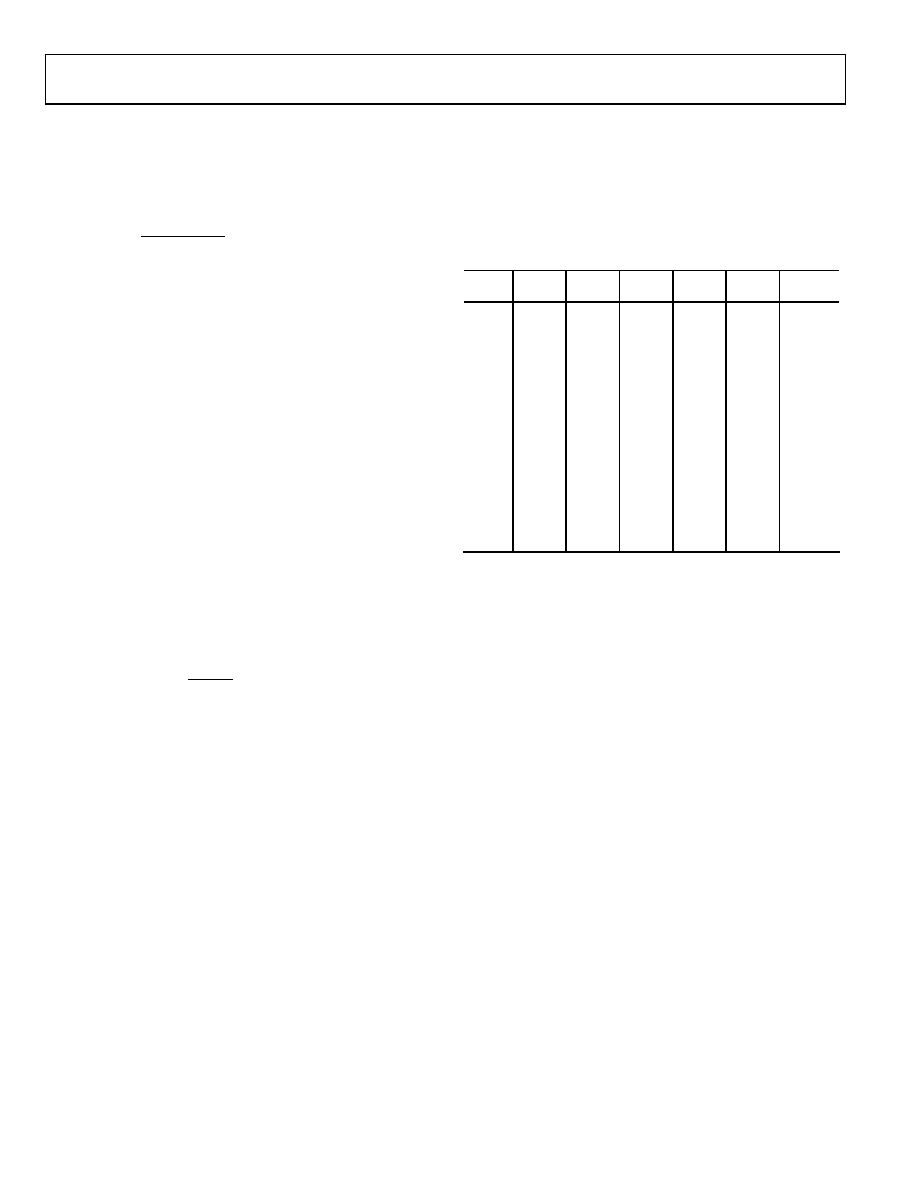

Table 4 illustrates the amount of bandwidth in percentage of

the data rate into the rCIC2 stage. The data in this table may be

scaled to any other allowable sample rate up to 65 MHz. The

table can be used as a tool to decide how to distribute the

decimation between rCIC2, CIC5, and the RC .

Example Calculations:

Goal:

Implement a filter with an input sample rate of 10 MHz,

OLrCIC2 is the output level from the rCIC2 stage expressed as a

fraction of the input_level. OLrCIC2 is used later in the CIC5

stage-level calculations.

RCIC2 REJECTION

F

requiring 100 dB of alias rejection for a ±7 kHz pass band.

Solution:

First determine the percentage of the sample rate that

is represented by the pass band, as follows:

07

.

0

10

7

100

=

×

=

MHz

kHz

BW

fraction

Then find the 100 dB column on the right of the table and

look down this column for a value greater than or equal to your

pass- and percentage of the clock rate. Then look across to the

extreme left column and find the corresponding rate change

factor (MrCIC2/LrCIC2). Referring to t e table, notice that for a

MrCIC2/LrCIC2 of 4, the frequency having 100 dB of alias

rCIC rate change is 4. A higher chosen MrCIC2/LrCIC2 means less

e 100 dB required.

consumed in subsequent stages. It should also be noted that

there is more than one way to get the decimation by 4. A

4, 2/8, or

lest

ble

C

lia

cti

le

= 1

ndw

ho

Per

ge o

IC2

/

IC2

B

dB

b

h

rejection is 0.071%, which is slightly greater than the 0.07%

calculated. Therefore, for this example, the maximum bound on

2

alias rejection than th

An M rCIC2/L rCIC2 of less than 4 would still yield the required

rejection; however, power consumption can be minimized by

decimating as much as possible in this rCIC2 stage. Decimation

in rCIC2 lowers the data rate, and thus reduces power

decimation of 4 is the same as an L/M ratio of 0.25. Thus, any

integer combination of L/M that yields 0.25 works (1/

4/16). However, for the best dynamic range, use the simp

. F

p

v

4

ratio or exam le, 1/4 gi es better performance than /16.

Ta

14. SSB r IC2 A

s Reje

on Tab (fSAMP

)

Ba

idth S

wn in

centa

f fSAMP

MrC

L rC

50 d

60 d

70 d

80 d

90

100

2

1.79

1.007

8

1

0.566

0.31

0.179

0.10

3

1.508

0.858

0.486

0.274

0.155

0.087

4

1.217

0.696

0.395

0.223

0.126

0.071

5

1.006

6

0.577

0.328

0.18

0.105

0.059

6

0.853

8

0.49

0.279

0.15

0.089

0.05

7

0.739

0.425

0.242

0.137

0.077

0.044

8

0.651

8

0.374

0.213

0.121

0.068

0.03

9

0.581

1

0.334

0.19

0.108

0.06

0.034

10

0.525

0.302

0.172

0.097

0.055

0.031

11

0.478

8

0.275

0.157

0.089

0.05

0.02

12

0.439

0.253

0.144

0.082

0.046

0.026

13

0.406

4

0.23

0.133

0.075

0.043

0.024

14

0.378

4

0.217

0.12

0.07

0.04

0.022

15

0.353

6

0.203

0.11

0.066

0.037

0.021

16

0.331

0.19

0.109

0.061

0.035

0.02

CIM

N

IN

O

ON

IST

C2 decimatio

es a

red

ist

0. This 12-bit

ister co ains t

cima

us 1

e int

-

po

s s

R

0x

his 9

lue

s

int

ion

mi

e.

IC2

LE

ST

ister 0x92 co

the

g i

atio

he

pr

fun

is t

h

val

pu

the

revious sections.

Bits 4–0 of this register should be written with the same values

as those written to Bits 9–5 to accommodate a redundant

internal hardware feature.

Bits 9–5 (SrCIC2) contain the 5-bit scaling factor for rCIC2.

Bits 11–10 are reserved and must be written low.

In applications that do not require the features of the rCIC2,

bypass it by setting the L/M ratio to 1/1. This effectively

bypasses all circuitry of the rCIC2 except the scaling, which is

still effectual.

DE

ATIO AND

TERP LATI

REG

ERS

rCI

n valu

re sto

in Reg er 0x9

reg

nt

he de

tion value min

. Th

erpola

tion

rtion i tored in egister

91. T

-bit va

hold

the

erpolat

value

nus on

RC

SCA

REGI

ER

Reg

ntains

scalin nform

n for t

rCIC2.

The

imary

ction

o store t e scale

ue com

ted in

p

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD7575JP-REEL | 1-CH 8-BIT SUCCESSIVE APPROXIMATION ADC, PARALLEL ACCESS, PQCC20 |

| AD7575KP-REEL | 1-CH 8-BIT SUCCESSIVE APPROXIMATION ADC, PARALLEL ACCESS, PQCC20 |

| AD7741YR-REEL7 | VOLTAGE-FREQUENCY CONVERTER, 6.144 MHz, PDSO8 |

| AD8402AR1-REEL | DUAL 1K DIGITAL POTENTIOMETER, 3-WIRE SERIAL CONTROL INTERFACE, 256 POSITIONS, PDSO14 |

| AD8402ARU100-REEL | DUAL 100K DIGITAL POTENTIOMETER, 3-WIRE SERIAL CONTROL INTERFACE, 256 POSITIONS, PDSO14 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD6653 | 制造商:AD 制造商全稱:Analog Devices 功能描述:IF Diversity Receiver |

| AD6653-125EBZ | 制造商:Analog Devices 功能描述:Evaluation Board For AD6653 制造商:Analog Devices 功能描述:EVAL BD FOR AD6653 - Bulk 制造商:Analog Devices 功能描述:KIT EVALUATION BOARD AD6653 |

| AD6653-150EBZ | 制造商:Analog Devices 功能描述:EVAL BD FOR AD6653 - Bulk |

| AD6653BCPZ-125 | 制造商:Analog Devices 功能描述:IF DIVERSITY RCVR 64LFCSP EP - Trays 制造商:Rochester Electronics LLC 功能描述: 制造商:Analog Devices 功能描述:IC RECEIVER IF DIVERSITY LFCSP64 |

| AD6653BCPZ-150 | 制造商:Analog Devices 功能描述:IF DIVERSITY RCVR 64LFCSP EP - Trays 制造商:Analog Devices 功能描述:IC RECEIVER IF DIVERSITY LFCSP64 制造商:Analog Devices 功能描述:IC, RECEIVER, IF DIVERSITY, LFCSP64 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。