- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄293971 > 5962R0722402VYC (ATMEL CORP) SPECIALTY MICROPROCESSOR CIRCUIT, PQFP256 PDF資料下載

參數(shù)資料

| 型號(hào): | 5962R0722402VYC |

| 廠商: | ATMEL CORP |

| 元件分類(lèi): | 微控制器/微處理器 |

| 英文描述: | SPECIALTY MICROPROCESSOR CIRCUIT, PQFP256 |

| 封裝: | QFP-256 |

| 文件頁(yè)數(shù): | 94/155頁(yè) |

| 文件大小: | 4139K |

| 代理商: | 5962R0722402VYC |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)當(dāng)前第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)

AT697F PRELIMINARY INFORMATION

43

7703D–AERO–12/09

PR

ELI

MINA

R

Y

IN

FOR

M

AT

IO

N

Cache

Memories

Overview

The AT697F processor implements a Harvard architecture with separate instruction and data

buses, connected to two independent cache controllers. In order to improve the speed perfor-

mance of the cpu core, multi-set-caches are used for both instruction and data caches.

The cache replacement policy used for both instruction and data caches is based on the LRU

algorithm. The least recently used (LRU) set of the cache is replaced when new data need to be

stored in cache.

Cache mapping

Most of the main memory areas can be cached. The cacheable areas are the PROM and RAM

areas. The following table presents the caching capabilities of the processor.

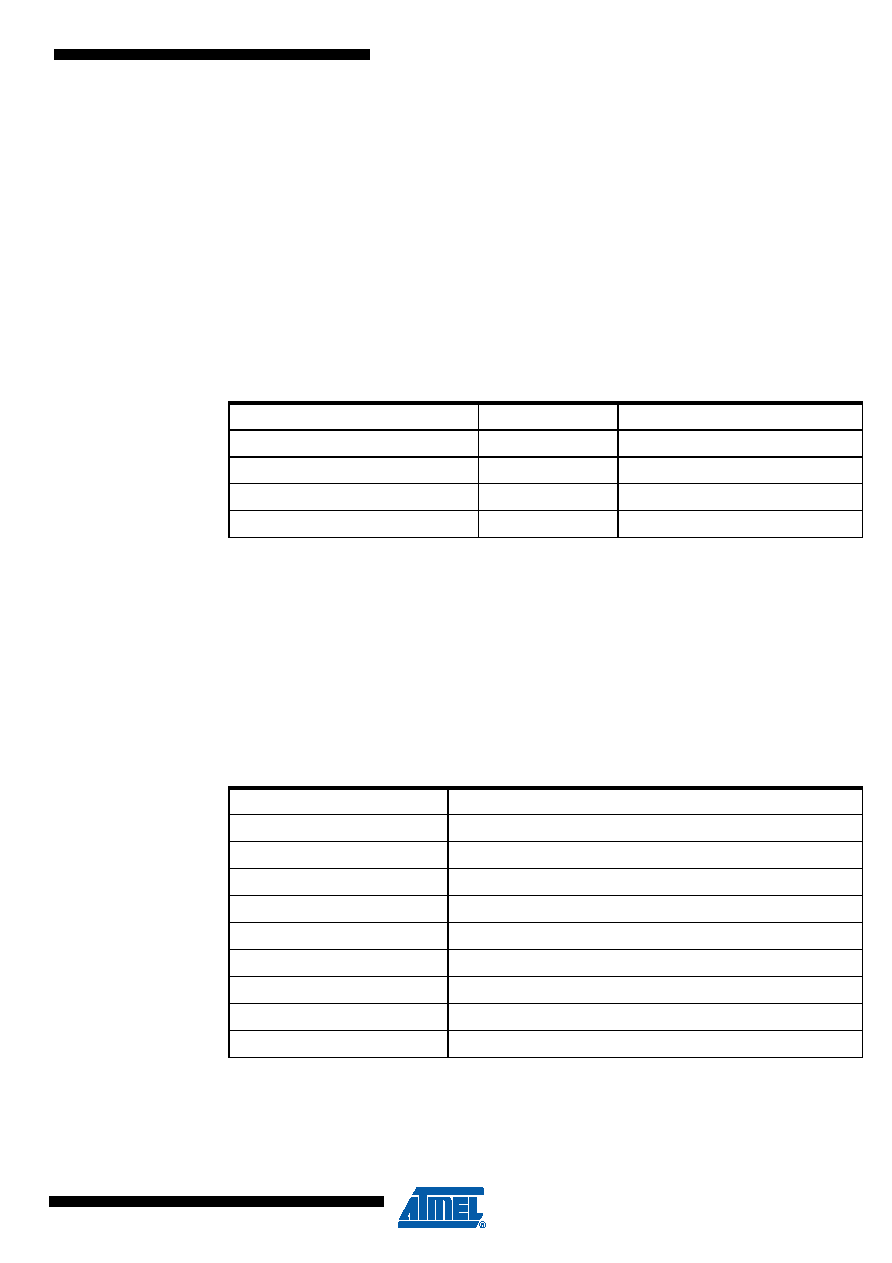

Table 17.

Address Range

Area

Cache status

0x00000000 - 0x1FFFFFFF

PROM

Cached

0x20000000 - 0x3FFFFFFF

I/O

Non-cacheable

0x40000000 -0x7FFFFFFF

RAM

Cached

0x80000000 -0xFFFFFFFF

Internal

Non-cacheable

Cache Capability List

Operation

During normal operation, the processor accesses instructions and data using ASI 0x8 - 0xB as

defined in the SPARC standard.

Using the LDA/STA instructions, alternative address spaces as caches can be accessed.

ASI[3:0] are used for the mapping when ASI[7:4] have no influence on operation.

Access with ASI 0 - 3 will force a cache miss, update the cache if the data was previously

cached or allocate a new line if the data was not in the cache and the address refers to a

cacheable location.

Access to ASI 4 and 7 will force a cache miss and update the cache if the data was

previously cached.

The following table shows the ASI implementation on the AT697F.

Table 18. ASI Usage

ASI

Usage

0x0, 0x1, 0x2, 0x3

Forced cache miss (replace if cacheable)

0x4, 0x7

Forced cache miss (update on hit)

0x5

Flush instruction cache

0x6

Flush data cache

0x8, 0x9, 0xA, 0xB

Normal cached access (replace if cacheable)

0xC

Instruction cache tags

0xD

Instruction cache data

0xE

Data cache tags

0xF

Data cache data

Note:

Please refer to the SPARC v8 specification for detailed information on ASI usage.

Instruction Cache

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 5962R8958702VXA | 5 V FIXED POSITIVE LDO REGULATOR, 1 V DROPOUT, CDSO16 |

| 5962R9215311VTA | 32K X 8 STANDARD SRAM, 55 ns, CDFP36 |

| 5962R9215311VTX | 32K X 8 STANDARD SRAM, 55 ns, CDFP36 |

| 5962G9215309VMX | 32K X 8 STANDARD SRAM, 55 ns, CDIP28 |

| 5962F9215315VMC | 32K X 8 STANDARD SRAM, 70 ns, CDIP28 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 5962R0722601VZA | 制造商:Texas Instruments 功能描述:D/A CONVERTER, 12-BIT - Trays |

| 5962R0722701VZA | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 8-Ch 50 kSPS-1 MSPS RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類(lèi)型:Differential 信噪比:107 dB 接口類(lèi)型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| 5962R0722902VXA | 功能描述:低壓差穩(wěn)壓器 - LDO 3-Terminal Adj Reg RoHS:否 制造商:Texas Instruments 最大輸入電壓:36 V 輸出電壓:1.4 V to 20.5 V 回動(dòng)電壓(最大值):307 mV 輸出電流:1 A 負(fù)載調(diào)節(jié):0.3 % 輸出端數(shù)量: 輸出類(lèi)型:Fixed 最大工作溫度:+ 125 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-20 |

| 5962R0722961VXA | 功能描述:低壓差穩(wěn)壓器 - LDO 3-Terminal Adj Reg RoHS:否 制造商:Texas Instruments 最大輸入電壓:36 V 輸出電壓:1.4 V to 20.5 V 回動(dòng)電壓(最大值):307 mV 輸出電流:1 A 負(fù)載調(diào)節(jié):0.3 % 輸出端數(shù)量: 輸出類(lèi)型:Fixed 最大工作溫度:+ 125 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-20 |

| 5962R0724902VPC | 制造商:Intersil Corporation 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。