- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄293971 > 5962R0722402VYC (ATMEL CORP) SPECIALTY MICROPROCESSOR CIRCUIT, PQFP256 PDF資料下載

參數(shù)資料

| 型號: | 5962R0722402VYC |

| 廠商: | ATMEL CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | SPECIALTY MICROPROCESSOR CIRCUIT, PQFP256 |

| 封裝: | QFP-256 |

| 文件頁數(shù): | 110/155頁 |

| 文件大小: | 4139K |

| 代理商: | 5962R0722402VYC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁當前第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁

58

7703D–AERO–12/09

AT697F PRELIMINARY INFORMATION

PR

ELI

MINA

R

Y

IN

FOR

M

AT

IO

N

UARTs (UART1

and UART2)

The Universal Asynchronous Receiver and Transmitter (UART) is a highly flexible serial commu-

nication module. The AT697 implements two uarts : UART1 and UART2. Uarts on the processor

are defined as alternate functions of the general purpose interface (GPI).

Overview

The two UART’s provide double buffering. Each UART consists of a transmitter holding register,

a receiver holding register, a transmitter shift register, and a receiver shift register. Each of these

registers are 8-bit wide.

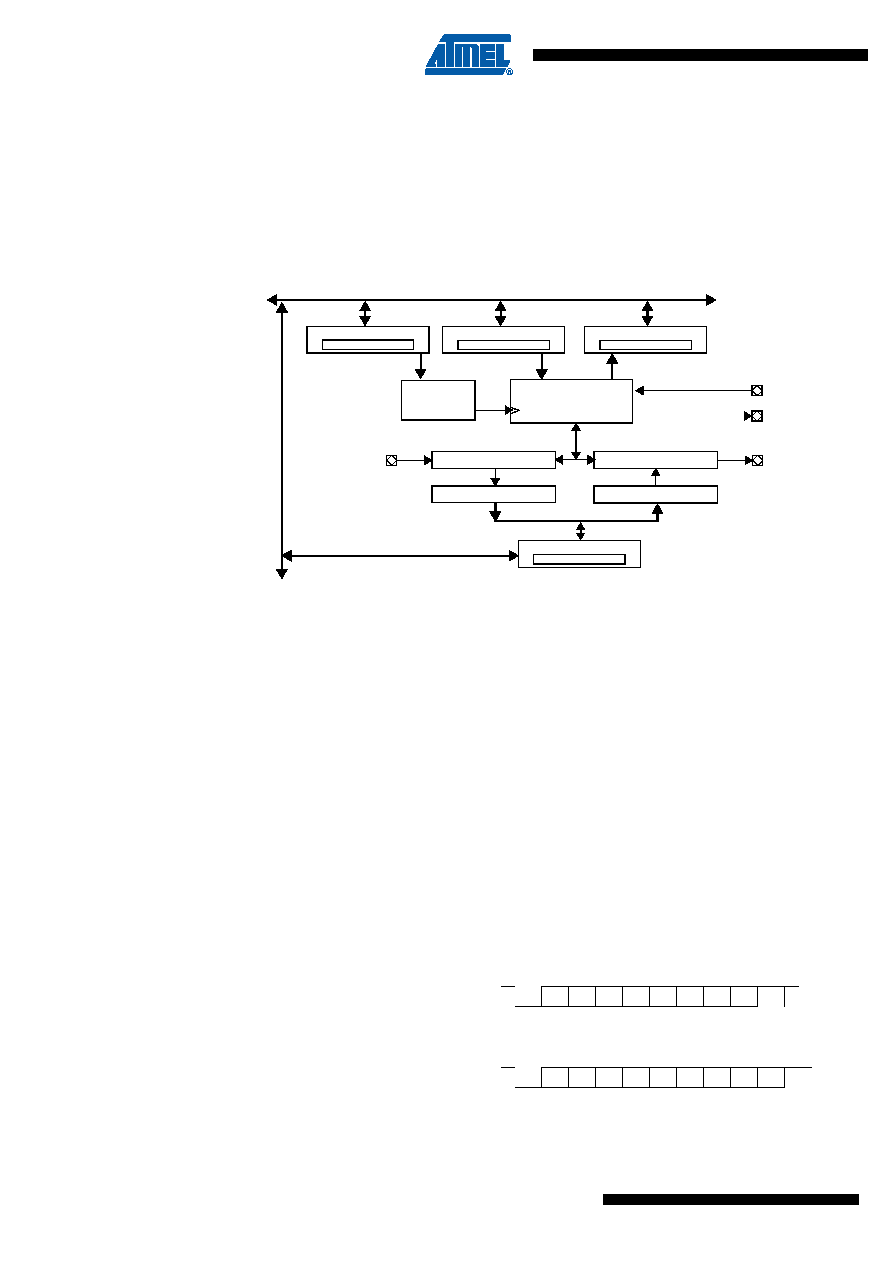

Figure 36. UART Block Diagram

RX

TX

CTS

RTS

Baud-rate

generator

Receiver Shift Register

Receiver Holding Register

Transmitter Shift Register

Transmitter Holding Register

Uart Status Reg.

UASn

Uart Scaler Reg.

UASCAn

Uart Data Reg.

Uart Control Reg.

UADn

UACn

control logic

Da

ta

Bu

s

Each UART is fully controlled by a set of four registers including :

a control register

a status register

a scaler register

and a data register

Serial Frame

A serial frame is defined to be one character of data bits with synchronisation bits (start and stop

bits), and optionnaly a parity bit for error checking.

Frame formats

Two frame formats are accepted by the AT697 UARTs, the only difference being the presence

or the absence of the parity bit. All the frames are built on an eight data bits basis.

A frame starts with the synchronization start bit followed by the least significant data bit. Then

the next data bits, up to a total of eight, are succeeding, ending with the most significant bit. If

enabled by setting the UACx PEx, the parity bit is inserted after the data bits and before the

stop bit.

The following figure illustrates the accepted frame formats.

Figure 37. Data frame format

Start D0

Stop

D6

D5

D4

D3

D2

D1

D7

Start D0

D6

D5

D4

D3

D2

D1

D7

Stop

Parity

Data frame, no parity:

Data frame with parity:

Parity bit

The parity bit is calculated by doing an exclusive-or of all the data bits. The odd parity is configured set-

ting logical one the UACx

PSx . In this case, the result of the exclusive or is inverted. An even parity can

be selected setting logical zero the UACx PSx.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 5962R8958702VXA | 5 V FIXED POSITIVE LDO REGULATOR, 1 V DROPOUT, CDSO16 |

| 5962R9215311VTA | 32K X 8 STANDARD SRAM, 55 ns, CDFP36 |

| 5962R9215311VTX | 32K X 8 STANDARD SRAM, 55 ns, CDFP36 |

| 5962G9215309VMX | 32K X 8 STANDARD SRAM, 55 ns, CDIP28 |

| 5962F9215315VMC | 32K X 8 STANDARD SRAM, 70 ns, CDIP28 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 5962R0722601VZA | 制造商:Texas Instruments 功能描述:D/A CONVERTER, 12-BIT - Trays |

| 5962R0722701VZA | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 8-Ch 50 kSPS-1 MSPS RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| 5962R0722902VXA | 功能描述:低壓差穩(wěn)壓器 - LDO 3-Terminal Adj Reg RoHS:否 制造商:Texas Instruments 最大輸入電壓:36 V 輸出電壓:1.4 V to 20.5 V 回動電壓(最大值):307 mV 輸出電流:1 A 負載調(diào)節(jié):0.3 % 輸出端數(shù)量: 輸出類型:Fixed 最大工作溫度:+ 125 C 安裝風格:SMD/SMT 封裝 / 箱體:VQFN-20 |

| 5962R0722961VXA | 功能描述:低壓差穩(wěn)壓器 - LDO 3-Terminal Adj Reg RoHS:否 制造商:Texas Instruments 最大輸入電壓:36 V 輸出電壓:1.4 V to 20.5 V 回動電壓(最大值):307 mV 輸出電流:1 A 負載調(diào)節(jié):0.3 % 輸出端數(shù)量: 輸出類型:Fixed 最大工作溫度:+ 125 C 安裝風格:SMD/SMT 封裝 / 箱體:VQFN-20 |

| 5962R0724902VPC | 制造商:Intersil Corporation 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。