- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372112 > SAA7108 (NXP Semiconductors N.V.) PC-CODEC PDF資料下載

參數(shù)資料

| 型號: | SAA7108 |

| 廠商: | NXP Semiconductors N.V. |

| 元件分類: | Codec |

| 英文描述: | PC-CODEC |

| 中文描述: | PC的編解碼器 |

| 文件頁數(shù): | 192/202頁 |

| 文件大小: | 983K |

| 代理商: | SAA7108 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁第179頁第180頁第181頁第182頁第183頁第184頁第185頁第186頁第187頁第188頁第189頁第190頁第191頁當(dāng)前第192頁第193頁第194頁第195頁第196頁第197頁第198頁第199頁第200頁第201頁第202頁

2004 Mar 16

192

Philips Semiconductors

Product specification

PC-CODEC

SAA7108E; SAA7109E

19.2

Audio clock generation part

The given values force the following behaviour of the SAA7108E; SAA7109E audio clock generation part:

Used crystal is 24.576 MHz

Expected field frequency is 59.94 Hz (e.g. NTSC M standard)

Generated audio master clock frequency at pin AMCLK is 256

×

44.1 kHz = 11.2896 MHz

AMCLK is externally connected to AMXCLK (short-cut between pins K12 and J12)

ASCLK = 32

×

44.1 kHz = 1.4112 MHz

ALRCLK is 44.1 kHz.

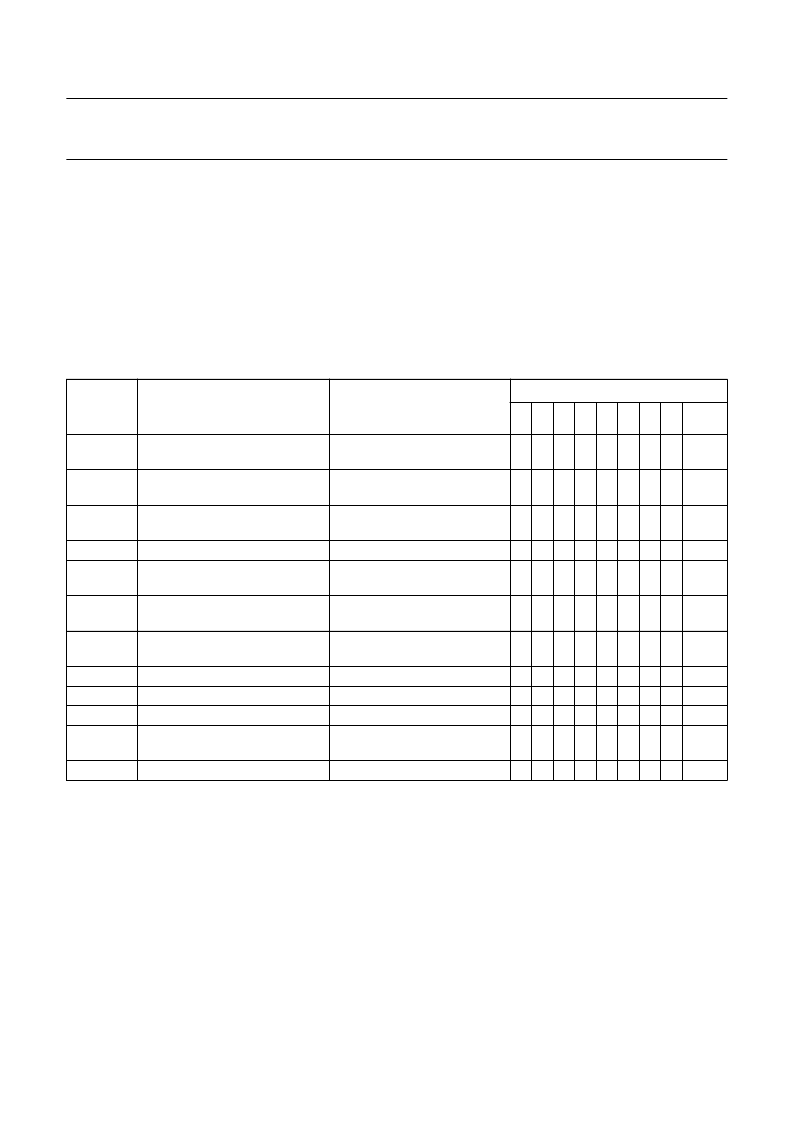

Table 240

Audio clock part set-up values

Note

1.

All X values must be set to logic 0.

SUB

ADDRESS

(HEX)

REGISTER FUNCTION

BIT NAME

(1)

START VALUES

7

6

5

4

3

2

1

0

HEX

30

audio master clock cycles per

field; bits 7 to 0

audio master clock cycles per

field; bits 15 to 8

audio master clock cycles per

field; bits 17 and 16

reserved

audio master clock nominal

increment; bits 7 to 0

audio master clock nominal

increment; bits 15 to 8

audio master clock nominal

increment; bits 21 to 16

reserved

clock ratio AMXCLK to ASCLK

clock ratio ASCLK to ALRCLK

audio clock generator basic

set-up

reserved

ACPF7 to ACPF0

1

0

1

1

1

1

0

0

BC

31

ACPF15 to ACPF8

1

1

0

1

1

1

1

1

DF

32

X, X, X, X, X, X, ACPF17 and

ACPF16

X, X, X, X, X, X, X, X

ACNI7 to ACNI0

0

0

0

0

0

0

1

0

02

33

34

0

1

0

1

0

0

0

0

0

1

0

1

0

0

0

1

00

CD

35

ACNI15 to ACNI8

1

1

0

0

1

1

0

0

CC

36

X, X, ACNI21 to ACNI16

0

0

1

1

1

0

1

0

3A

37

38

39

3A

X, X, X, X, X, X, X, X

X, X, SDIV5 to SDIV0

X, X, LRDIV5 to LRDIV0

X, X, X, X, APLL, AMVR,

LRPH, SCPH

X, X, X, X, X, X, X, X

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

1

0

0

0

1

0

0

00

03

10

00

3B to 3F

0

0

0

0

0

0

0

0

00

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SAA7109 | PC-CODEC |

| SAA7108E | PC-CODEC |

| SAA7109E | PC-CODEC |

| SAA7108AE | HD-CODEC |

| SAA7109A | HD-CODEC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SAA7108AE | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:HD-CODEC |

| SAA7108E | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:PC-CODEC |

| SAA7109 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:PC-CODEC |

| SAA7109A | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:HD-CODEC |

| SAA7109AE | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:HD-CODEC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。