- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄359147 > MC72000 (飛思卡爾半導(dǎo)體(中國(guó))有限公司) Integrated Bluetooth Radio PDF資料下載

參數(shù)資料

| 型號(hào): | MC72000 |

| 廠商: | 飛思卡爾半導(dǎo)體(中國(guó))有限公司 |

| 英文描述: | Integrated Bluetooth Radio |

| 中文描述: | 集成藍(lán)牙無(wú)線 |

| 文件頁(yè)數(shù): | 108/156頁(yè) |

| 文件大?。?/td> | 1782K |

| 代理商: | MC72000 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)當(dāng)前第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)

108

MC72000 Advance Information Data Sheet

Go to: www.freescale.com

MOTOROLA

Hardware Functional Description

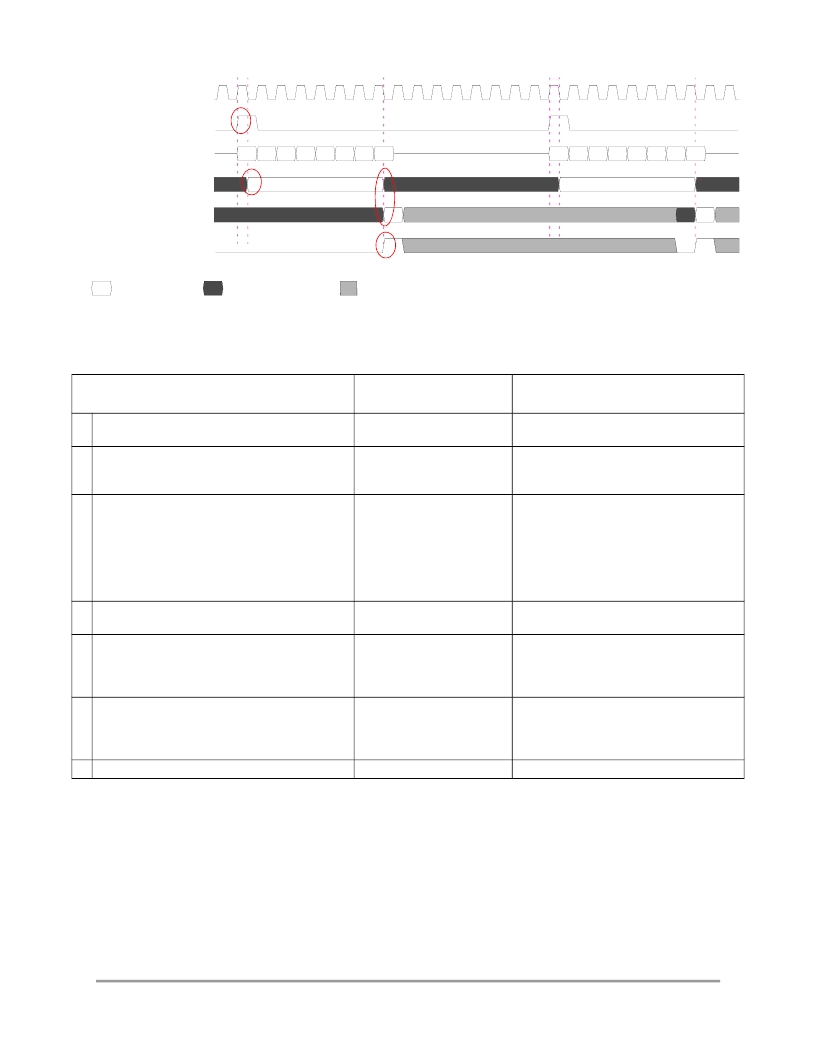

Figure 72. Normal Mode Receive Timing—Continuous Clock (WL=8-bit words, DC=1)

Table 53. Normal Mode Receive Operations

Step

RXFIFO Disabled

(See Figure 72)

RXFIFO Enabled

(No Figure Available

1

Leading edge of frame sync occurs on the

SRFS pin

Falling edge of receive clock occurs on the

SRCK pin and the next bit of data is shifted into

the RXSR register

When WL bits (see Section 7.4.5.2.7, “SSI

Transmit and Receive Control Registers

(STXCR, SRXCR)”) have been received RXSR

contents are transferred to the SRX register on

the next falling edge of the receive clock

Note: The SRX register is actually loaded during

the middle of the last receive bit.

Flag status update

2

3

4

The RDR bit is set

The RFF bit is set if the level of data in the

RXFIFO rises above the watermark level

Receive interrupt occurs when RFF set

5

If the RIE bit is set, enabling receive interrupts,

then:

(Other options for processing the data transfer

is either polling or DMA transfers.)

Receive over-run (setting the ROE bit of the

SCSR register) is prevented by

1

:

Receive interrupt occurs

when RDR set

6

1.See the description of the ROE bit in

Section 7.4.5.2.8, “SSI Control/Status Register (SCSR)”

for a description of what

happens when the ROE bit is set.

2.The frame sync must not occur earlier than what is configured in the SRXCR as documented in Section 7.4.5.2.7, “SSI

Transmit and Receive Control Registers (STXCR, SRXCR).”

Data is read from the SRX

before the RXSR tries to

write new transmit data at

the next frame sync

Data is read from the SRX before the

RXSR tries to provide more data to a full

RXFIFO (it can take several frame times

to fill the RXFIFO)

7 Repeat at step 1 on the next frame sync

2

Continuous SRCK

SRFS

SRXD

RXSR register

SRX register

RDR status bit/interrupt

Valid

Indefinite transition depends on SW interrupt processing

Invalid

1

2

3

4

F

For More Information On This Product,

n

.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC7445ARX1000LF | RISC Microprocessor Hardware Specifications |

| MC7445ARX1000LG | RISC Microprocessor Hardware Specifications |

| MC7447A | PowerPC microprocessor |

| MC7447AHX1000NB | PowerPC microprocessor |

| MC7447AHX1167NB | PowerPC microprocessor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC7220C-100M RI-BLK | 制造商:Farnell / Pro-Power 功能描述:CABLE DEF 7-2-20C 20CORE 100M 制造商:pro-power 功能描述:CABLE, DEF 7-2-20C, 20CORE, 100M 制造商:pro-power 功能描述:CABLE, DEF 7-2-20C, 20CORE, 100M; Reel Length (Imperial):328ft; Reel Length (Metric):100m; No. of Conductors:20; Voltage Rating:440V; No. of Strands x Strand Size:7 x 0.2mm; Conductor Area CSA:0.22mm2; Jacket Colour:Black; Jacket ;RoHS Compliant: Yes |

| MC7220C-100M RI-BLK | 制造商:Farnell / Pro-Power 功能描述:CABLE DEF 7-2-20C 20 CORE 100M |

| MC7220C-25M RI-BLK | 制造商:Farnell / Pro-Power 功能描述:CABLE DEF 7-2-20C 20CORE 25M 制造商:pro-power 功能描述:CABLE, DEF 7-2-20C, 20CORE, 25M |

| MC7220C-25M RI-BLK | 制造商:Farnell / Pro-Power 功能描述:CABLE DEF 7-2-20C 20 CORE 25M |

| MC7225C-25M RI-BLK | 制造商:Farnell / Pro-Power 功能描述:CABLE DEF 7-2-25C 25CORE 25M 制造商:pro-power 功能描述:MULTICORE, 25, 7/0.2MM, 25M, BLACK 制造商:pro-power 功能描述:CABLE, DEF 7-2-25C, 25CORE, 25M 制造商:PRIVATE LABEL 功能描述:CABLE, DEF 7-2-25C, 25CORE, 25M, Reel Length (Imperial):82ft, Reel Length (Metri |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。