- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369884 > LXP710PE Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 PDF資料下載

參數(shù)資料

| 型號(hào): | LXP710PE |

| 元件分類: | 通信及網(wǎng)絡(luò) |

| 英文描述: | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| 中文描述: | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| 文件頁(yè)數(shù): | 37/84頁(yè) |

| 文件大小: | 1108K |

| 代理商: | LXP710PE |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)當(dāng)前第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)

HDSL Framer/Mapper for 1168 kbps Applications

—

LXP710

Datasheet

37

General Interrupt Enable Register

Address: 1B

Abbreviation: GENINTEN

Read/Write

General Interrupt Vector Status

All of the HDSL overhead status bits in this register are latched active High when detected, and

remain High until a write is done by the microprocessor. When a logic

‘

1

’

is written to these

registers, these status bits are cleared unless the associated overhead bit is still active.

Address: 1C

Abbreviation: GENINTSTAT

Read/Write

2

LPREV[2]

0

000: Directs Loop 1 data to Loop 1 buffer and Loop 2 data to Loop 2 buffer.

001: Directs Loop 1 data to Loop 2 buffer and Loop 2 data to Loop 1 buffer.

010: Directs Loop 1 data to Loop 2 buffer and Loop 2 data to Loop 3 buffer.

011: Directs Loop 1 data to Loop 3 buffer and Loop 2 data to Loop 2 buffer.

100: Directs Loop 1 data to Loop 3 buffer and Loop 2 data to Loop 1 buffer.

101: Directs Loop 1 data to Loop 1 buffer and Loop 2 data to Loop 3 buffer.

1

LPREV[1]

0

0

LPREV[0]

0

Table 28. Loop Reversal Status Register (Continued)

Bit

Name

Default

Description

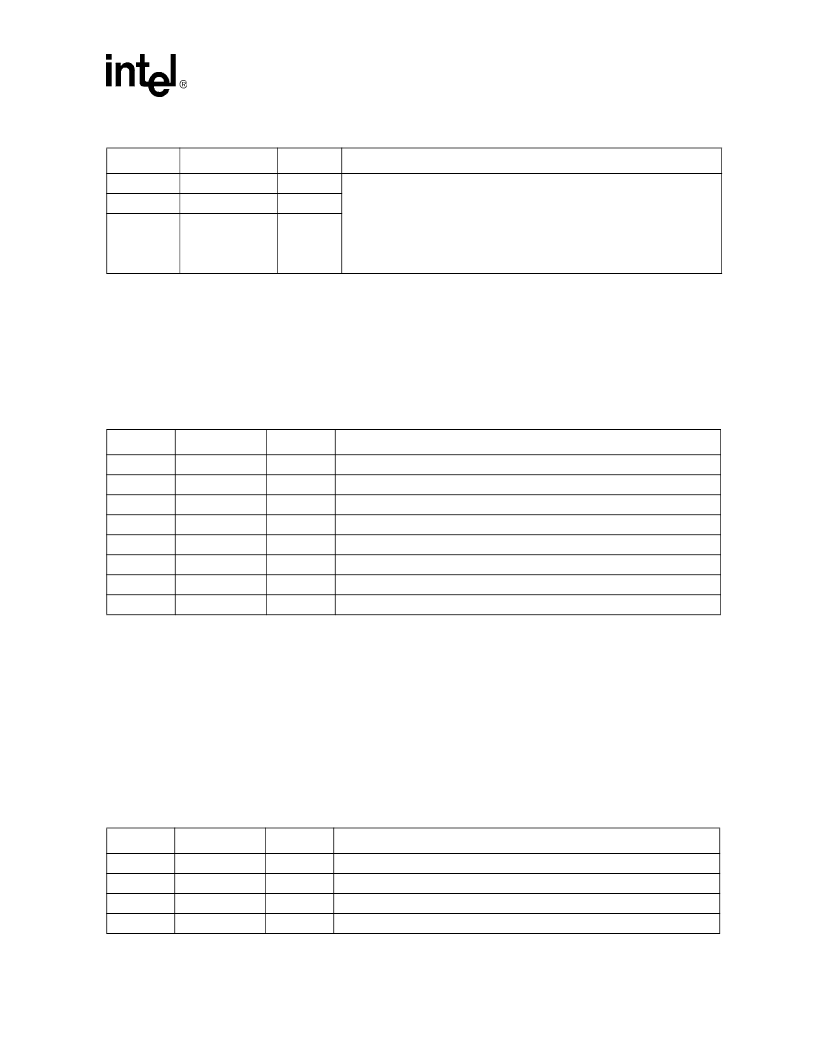

Table 29. General Interrupt Enable Register

Bit

Name

Default

Description

7

n/a

0

Not used; Always read Low.

6

EIPATLOS

0

Enable interrupt on pattern sync loss.

5

EIECOVR

0

Enable Interrupt on pattern error counter overflow.

4

EILOSD

0

Enable interrupt on demux loop 1 or loop 2 or loop 3 LOSD.

3

EIPS

0

Enable interrupt on demux loop power status indication.

2

EIL3INDC_R

0

Enable interrupt on demux loop 3 indc/indr bit active.

1

EIL2INDC_R

0

Enable interrupt on demux loop 2 indc/indr bit active.

0

EIL1INDC_R

0

Enable interrupt on demux loop 1 indc/indr bit active.

Table 30. General Interrupt Status Register

Bit

Name

Default

Description

7

n/a

0

Not used; Always read Low.

6

IVPATLOS

0

Pattern sync loss.

5

IVECOVR

0

Pattern error counter overflow.

4

IVLOSD

0

Demux loop 1 or loop 2 or loop 3 LOSD.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LXP730LE | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| LXT1000 | LAN TRANSCEIVER|SINGLE|HYBRID|BGA|492PIN|PLASTIC |

| LXT19908 | Amplifier. Other |

| LXT300JE | PCM Transceiver |

| LXT300NE | PCM Transceiver |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LXP730 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Multi-Rate DSL Framer |

| LXP730LE | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:FRAMER/FORMATTER|CMOS|QFP|64PIN|PLASTIC |

| LXP80 | 制造商:Johnson Components 功能描述: |

| LXPB2SA-50SB-Q | 制造商:SMC Corporation of America 功能描述:Actuator, electric, ball bushing |

| LXPH0000 | 制造商:Red Lion Controls 功能描述:ANNUNCIATOR LABELS, 1 LPAX LABEL: PH 制造商:Red Lion Controls 功能描述:1 LPAX LABEL PH |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。