- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383185 > IT8673F (Electronic Theatre Controls, Inc.) GT 35C 35#12 SKT PLUG PDF資料下載

參數(shù)資料

| 型號: | IT8673F |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | GT 35C 35#12 SKT PLUG |

| 中文描述: | 先進(jìn)的輸入/輸出(高級I / O)的初步規(guī)范V0.5 |

| 文件頁數(shù): | 62/128頁 |

| 文件大?。?/td> | 780K |

| 代理商: | IT8673F |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁當(dāng)前第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁

IT8673F

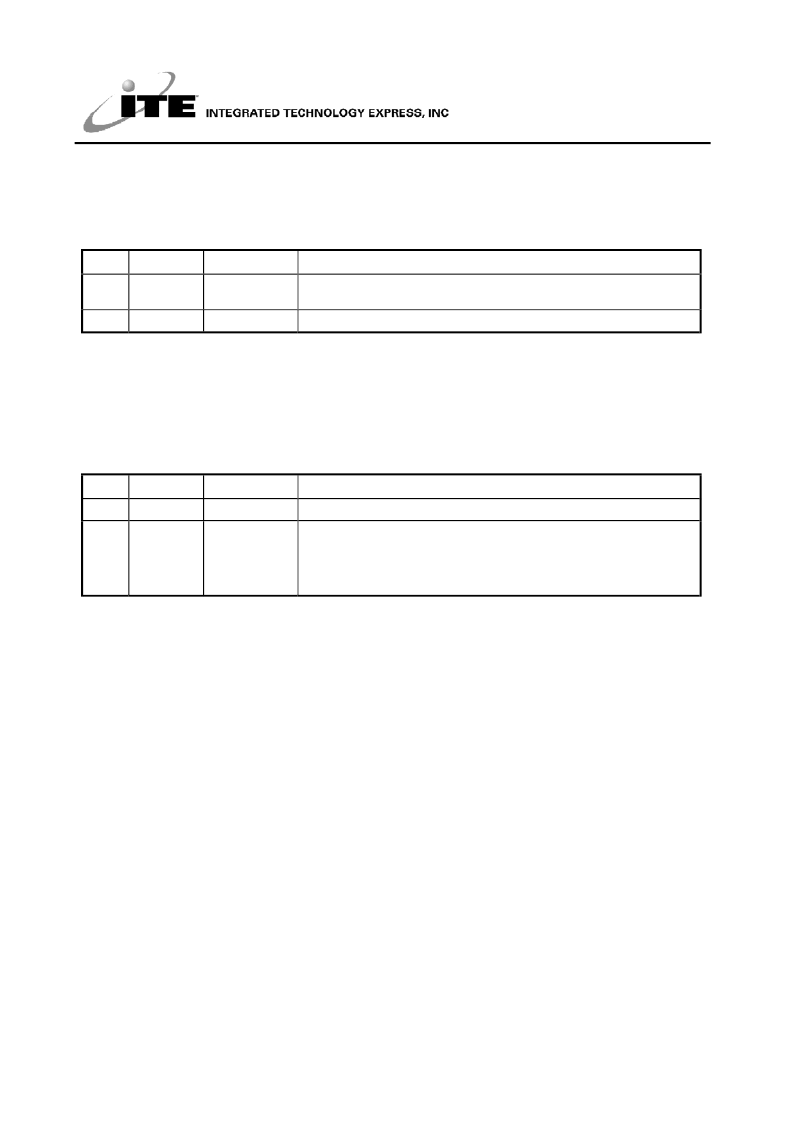

11.4.8.6 Digital Input Register (DIR, FDC Base Address + 07h)

2

52

This is a

read only

register and shares this address with the Diskette Control Register (DCR).

Table 11-8. Digital Input Register (DIR)

Bit

Symbol

Name

Description

7

DSKCHG

Diskette

Change

Indicates the inverting value of the bit monitored from the input of the Floppy

Disk Change pin (DSKCHG#).

6-0

NU

Not Used

-

11.4.8.7 Diskette Control Register (DCR, FDC Base Address + 07h)

This is a

write only

register and shares this address with the Digital Input Register (DIR).

The DCR register controls the data transfer rate for the FDC.

Table 11-9. Diskette Control Register (DCR)

Bit

Symbol

Name

Description

7-2

NU

Not Used

-

1-0

DRATE1-0

Data Rate

Select

Bits 1-0

00

01

10

11

Data Transfer Rate

500Kbps

300Kbps

250Kbps

1Mbps

11.4.9 Controller Phases

The FDC handles data transfer and control commands in three phases: Command, Execution and Result.

Not all commands utilize all these three phases.

11.4.9.1 Command Phase

Upon reset, the FDC enters the Command phase and is ready to receive commands from the host. The

host must verify that MSR bit 7 (RQM) = 1 and MSR bit 6 (DIO) = 0, indicating the FDC is ready to receive

data. For each command, a defined set of command code and parameter bytes must be transferred to the

FDC in a given order. See 11.4.11 and 11.4.12 for details on the various commands. RQM is set false (0)

after each byte-Read cycle, and set true (1) when a new parameter byte is required. The Command phase

is completed when this set of bytes has been received by the FDC. The FDC automatically enters the next

controller phase and the FIFO is disabled.

11.4.9.2 Execution Phase

Upon the completion of the Command phase, the FDC enters the Execution phase. It is in this phase that all

data transfers occur between the host and the FDC. The SPECIFY command indicates whether this data

transfer occurs in DMA or non-DMA mode. Each data byte is transferred via an IRQx or DRQx# based upon

the DMA mode. On reset, the CONFIGURE command can automatically enable or disable the FIFO. The

Execution phase is completed when all data bytes have been received. If the command executed does not

require a Result phase, the FDC is ready to receive the next command.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IT8687R | GT 35C 35#12 SKT PLUG |

| ITC1000 | GT 85C 85#16 SKT PLUG |

| ITF86130SK8T | N-Channel, Logic Level, Power MOSFET(N溝道邏輯電平功率MOS場效應(yīng)管) |

| ITF86182SK8T | 11A, 30V, 0.0115 Ohm, P-Channel, Logic Level, Power MOSFET |

| ITF87012SVT | 6A, 20V, 0.035 Ohm, N-Channel,2.5V Specified Power MOSFET(6A, 20V, 0.035Ω N溝道2.5V專用功率MOS場效應(yīng)管) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IT8687R | 制造商:ITE 功能描述: |

| IT86B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:TRIAC|600V V(DRM)|8A I(T)RMS|TO-220 |

| IT86C | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:TRIAC|600V V(DRM)|8A I(T)RMS|TO-220 |

| IT86F | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:TRIAC|600V V(DRM)|8A I(T)RMS|TO-220 |

| IT86G | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:TRIAC|600V V(DRM)|8A I(T)RMS|TO-220 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。