- 您現(xiàn)在的位置:買賣IC網 > PDF目錄358635 > 38D5 (Renesas Technology Corp.) SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER PDF資料下載

參數(shù)資料

| 型號: | 38D5 |

| 廠商: | Renesas Technology Corp. |

| 英文描述: | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| 中文描述: | 單芯片8位CMOS微機 |

| 文件頁數(shù): | 43/141頁 |

| 文件大小: | 2027K |

| 代理商: | 38D5 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁當前第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁

Rev.3.01

REJ03B0158-0301

Aug 08, 2007

Page 43 of 134

38D5 Group

SERIAL INTERFACE

SERIAL I/O1

Serial I/O1 can be used as either clock synchronous or

asynchronous (UART) serial I/O. A dedicated timer is also

provided for baud rate generation.

(1) Clock Synchronous Serial I/O Mode

Clock synchronous serial I/O1 mode can be selected by setting

the serial I/O mode selection bit of the serial I/O1 control register

to “1”.

For clock synchronous serial I/O1, the transmitter and the

receiver must use the same clock. If an internal clock is used,

transfer is started by a write signal to the TB/RB.

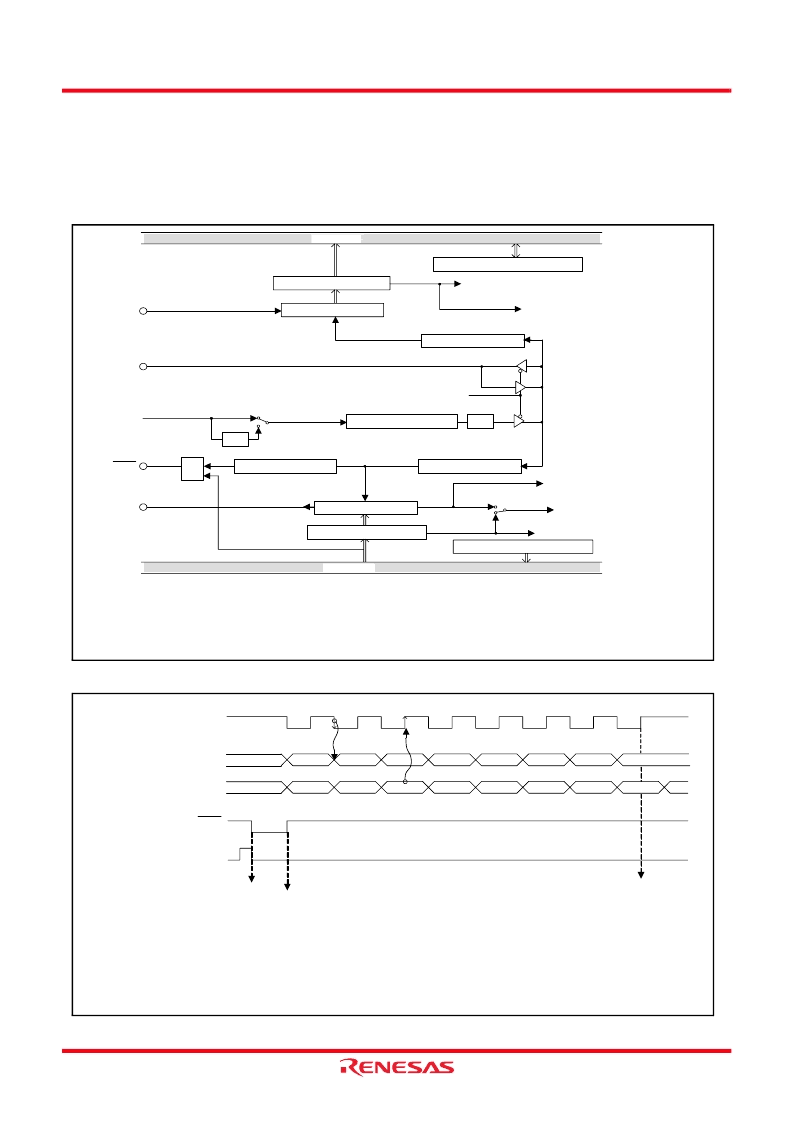

Fig. 33 Block diagram of clock synchronous serial I/O1

Fig. 34 Operation of clock synchronous serial I/O1 function

1/4

1/4

F/F

Receive buffer register

Receive shift register

Receive buffer full flag (RBF)

Receive interrupt request (RI)

Clock control circuit

Shift clock

Serial I/O1 synchronous

clock selection bit

Frequency division ratio 1/(n+1)

Baud rate generator

Address 001C

16

BRG count source selection bit

Clock control circuit

Falling-edge detector

Transmit buffer register

Data bus

Shift clock

Transmit shift completion flag (TSC)

Transmit buffer empty flag (TBE)

Serial I/O1 status register

Transmit interrupt request (TI)

Transmit interrupt source selection bit

Data bus

Transmit shift register

Serial I/O1 control register

Address 0018

16

Address 0018

16

Address 0019

16

Address 001A

16

P4

0

/R

X

D

P4

2

/S

CLK1

P4

3

/S

RDY1

P4

1

/T

X

D

φ

SOURCE

Note1:

φ

SOURCE indicates the followings:

X

IN

input in the frequency/2, 4, or 8 mode

On-chip oscillator divided by 4 in the on-chip oscillator mode

Sub-clock in the low-speed mode

(1)

D

7

D

0

D

1

D

2

D

3

D

4

D

5

D

6

D

0

D

1

D

2

D

3

D

4

D

5

D

6

RBF = 1

TSC = 1

TBE = 0

TBE = 1

TSC = 0

Transfer shift clock

(1/2 to 1/2048 of the internal

clock, or an external clock)

Serial output TxD

Serial input RxD

Write pulse to receive/transmit

buffer register

Overrun error (OE)

detection

Notes 1

: As the transmit interrupt (TI) source, which can be selected, either when the transmit buffer has emptied (TBE = 1) or

after the transmit shift operation has ended (TSC = 1), by setting the transmit interrupt source selection bit (TIC) of the

serial I/O1 control register.

2

: If data is written to the transmit buffer register when TSC=0, the transmit clock is generated continuously and serial data

is output continuously from the TxD pin.

3

: The receive interrupt (RI) is set when the receive buffer full flag (RBF) becomes “1” .

Receive enable signal S

RDY

D

7

相關PDF資料 |

PDF描述 |

|---|---|

| 38F1222 | 300mA LDO Linear Regulators with Internal Microprocessor Reset Circuit |

| TA5M | STECKER DIN MINI 5POL |

| 70B5031 | KUPPLUNG DIN MINI 5POL |

| 39-26-3050 | 300mA LDO Linear Regulators with Internal Microprocessor Reset Circuit |

| 390KD05JX | 11 to 460 Volts Varistor 0.7 to 29 Joule |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| 38D5_07 | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:Standard Characteristics Example |

| 38D5_08 | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| 38D511G015FE6AD | 制造商:Sprague/Vishay 功能描述:AL015X751 |

| 38D5-FMV | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:Standard Characteristics (Flash Memory Version) |

| 38DDP11B11M1QT | 功能描述:SWITCH PUSH DPDT,O-N-O,N,SL,LF , 制造商:grayhill inc. 系列:* 零件狀態(tài):在售 標準包裝:1 |

發(fā)布緊急采購,3分鐘左右您將得到回復。