- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄358635 > 38D5 (Renesas Technology Corp.) SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER PDF資料下載

參數(shù)資料

| 型號: | 38D5 |

| 廠商: | Renesas Technology Corp. |

| 英文描述: | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| 中文描述: | 單芯片8位CMOS微機 |

| 文件頁數(shù): | 39/141頁 |

| 文件大小: | 2027K |

| 代理商: | 38D5 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁當(dāng)前第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁

Rev.3.01

REJ03B0158-0301

Aug 08, 2007

Page 39 of 134

38D5 Group

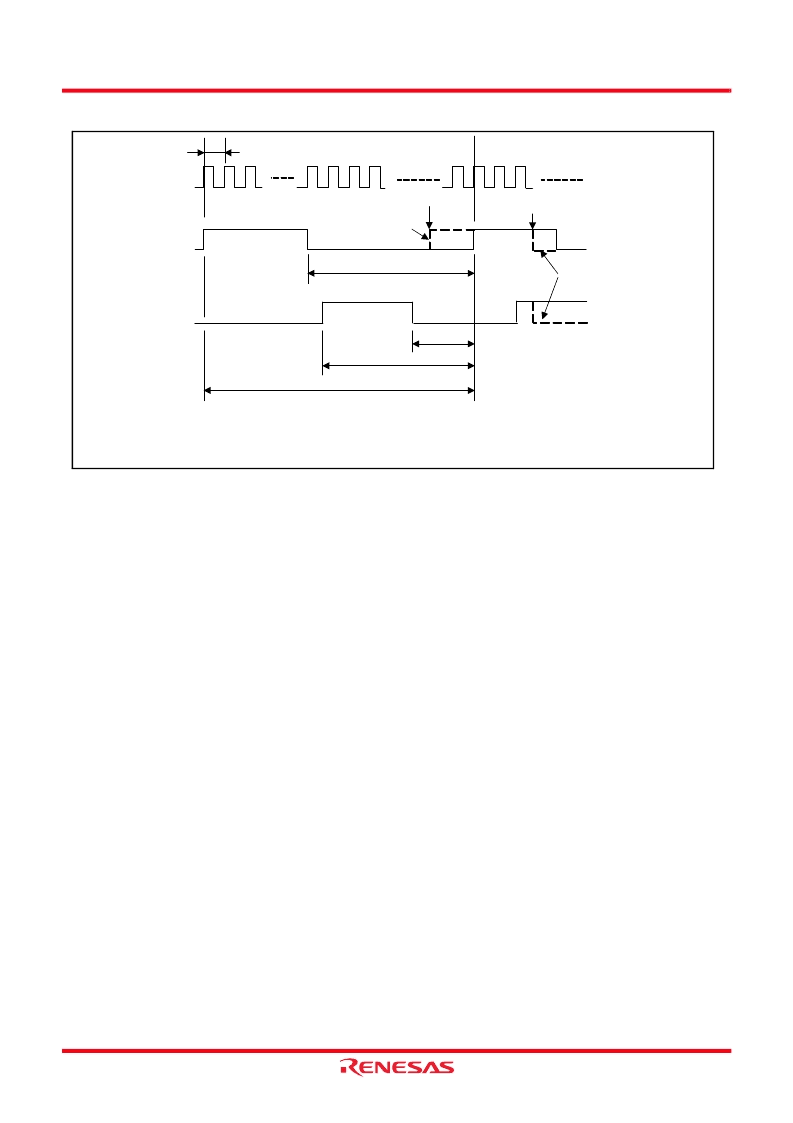

Fig. 29 Waveform of PWM/IGBT

<Notes on Timer X>

(1) Write Order to Timer X

In the timer mode, pulse output mode, event counter mode and

pulse width measurement mode, write to the following

registers in the order as shown below;

the timer X register (extension),

the timer X register (low-order),

the timer X register (high-order).

Do not write to only one of them.

When the above mode is set and timer X operates as the 16-bit

counter, if the timer X register (extension) is never set after

reset is released, setting the timer X register (extension) is not

required. In this case, write the timer X register (low-order)

first and the timer X register (high-order). However, once

writing to the timer X register (extension) is executed, note that

the value is retained to the reload latch.

Write to the timer X register by the 16-bit unit. Do not read the

timer X register while write operation is performed. If the

write operation is not completed, normal operation will not be

performed.

In the IGBT output and PWM modes, do not write “1” to the

timer X register (extension). Also, when “1” is already written

to the timer X register, be sure to write “0” to the register

before using.

Write to the following registers in the order as shown below;

the compare registers 1, 2, 3 (high- and low-order),

the timer X register (extension),

the timer X register (low-order),

the timer X register (high-order).

It is possible to use whichever order to write to the compare

registers 1, 2, 3 (high- and low-order). However, write both the

compare registers 1, 2, 3 and the timer X register at the same

time.

For the compare registers, set a value less than the setting value

in the timer X register. Also, do not set “00

16

”.

(2) Read Order to Timer X

In all modes, read the following registers in the order as shown

below;

the timer X register (extension),

the timer X register (high-order),

the timer X register (low-order).

When reading the timer X register (extension) is not required,

read the timer X register (high-order) first and the timer X

register (low-order).

Read order to the compare registers 1, 2, 3 is not specified.

Read from the timer X register by the 16-bit unit. Do not write

to the timer X register while read operation is performed. If the

read operation is not completed, normal operation will not be

performed.

(3) Write to Timer X

Which write control can be selected by the timer X write

control bit (b3) of the timer X mode register (address 2D

16

),

writing data to both the latch and the timer at the same time or

writing data only to the latch. When writing a value to the

timer X address to write to the latch only, the value is set into

the reload latch and the timer is updated at the next underflow.

After reset release, when writing a value to the timer X

address, the value is set into the timer and the timer latch at the

same time, because they are written at the same time.

When writing to the latch only, if the write timing to the high-

order reload latch and the underflow timing are almost the

same, the value is set into the timer and the timer latch at the

same time. In this time, counting is stopped during writing to

the high-order reload latch.

Switch the frequency division or count source* while the timer

count is stopped.

*This also applies when the frequency divider output is selected

as the timer count source and the count source is switched in

conjunction with a transition between operating modes (on-

chip oscillator mode, X

IN

mode, or low-speed mode). Be

careful when changing settings in the CPU mode register.

t

s

Timer X count source

Timer X PWM mode

IGBT output mode

m

×

ts

(n+1)

×

ts

The following PWM waveform is output;

Duty of T

XOUT1

output :{(n+1)-m}/(n+1),

Duty of T

XOUT2

output :(p-q)/(n+1),

Period :(n+1)

×

ts

T

XOUT1

output

(TXCON1 bit 5 = “0”)

T

XOUT2

output

(TXCON2 bit 1 = “0”)

q

×

ts

p

×

ts

n : Timer X setting value

m: Compare register 1 setting value

p : Compare register 2 setting value

q : Compare register 3 setting value

ts: One period of timer X count source

External trigger (INT

0

source)

is generated.

Level is “H” only IGBT

output mode.

INT

1

or INT

2

source is generated.

Level is forcibly “L” only IGBT

output mode.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 38F1222 | 300mA LDO Linear Regulators with Internal Microprocessor Reset Circuit |

| TA5M | STECKER DIN MINI 5POL |

| 70B5031 | KUPPLUNG DIN MINI 5POL |

| 39-26-3050 | 300mA LDO Linear Regulators with Internal Microprocessor Reset Circuit |

| 390KD05JX | 11 to 460 Volts Varistor 0.7 to 29 Joule |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 38D5_07 | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:Standard Characteristics Example |

| 38D5_08 | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| 38D511G015FE6AD | 制造商:Sprague/Vishay 功能描述:AL015X751 |

| 38D5-FMV | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:Standard Characteristics (Flash Memory Version) |

| 38DDP11B11M1QT | 功能描述:SWITCH PUSH DPDT,O-N-O,N,SL,LF , 制造商:grayhill inc. 系列:* 零件狀態(tài):在售 標(biāo)準(zhǔn)包裝:1 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。