- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄116319 > 531AA823M000DG (SILICON LABORATORIES) CRYSTAL OSCILLATOR, CLOCK, 823 MHz, LVPECL OUTPUT PDF資料下載

參數(shù)資料

| 型號(hào): | 531AA823M000DG |

| 廠商: | SILICON LABORATORIES |

| 元件分類: | XO, clock |

| 英文描述: | CRYSTAL OSCILLATOR, CLOCK, 823 MHz, LVPECL OUTPUT |

| 封裝: | ROHS COMPLIANT, SMD, 6 PIN |

| 文件頁數(shù): | 6/12頁 |

| 文件大?。?/td> | 215K |

| 代理商: | 531AA823M000DG |

Si530/531

Rev. 1.1

3

Total Stability

Temp stability = ±7 ppm

—

±20

ppm

Temp stability = ±20 ppm

—

±31.5

ppm

Temp stability = ±50 ppm

—

±61.5

ppm

Powerup Time4

tOSC

——

10

ms

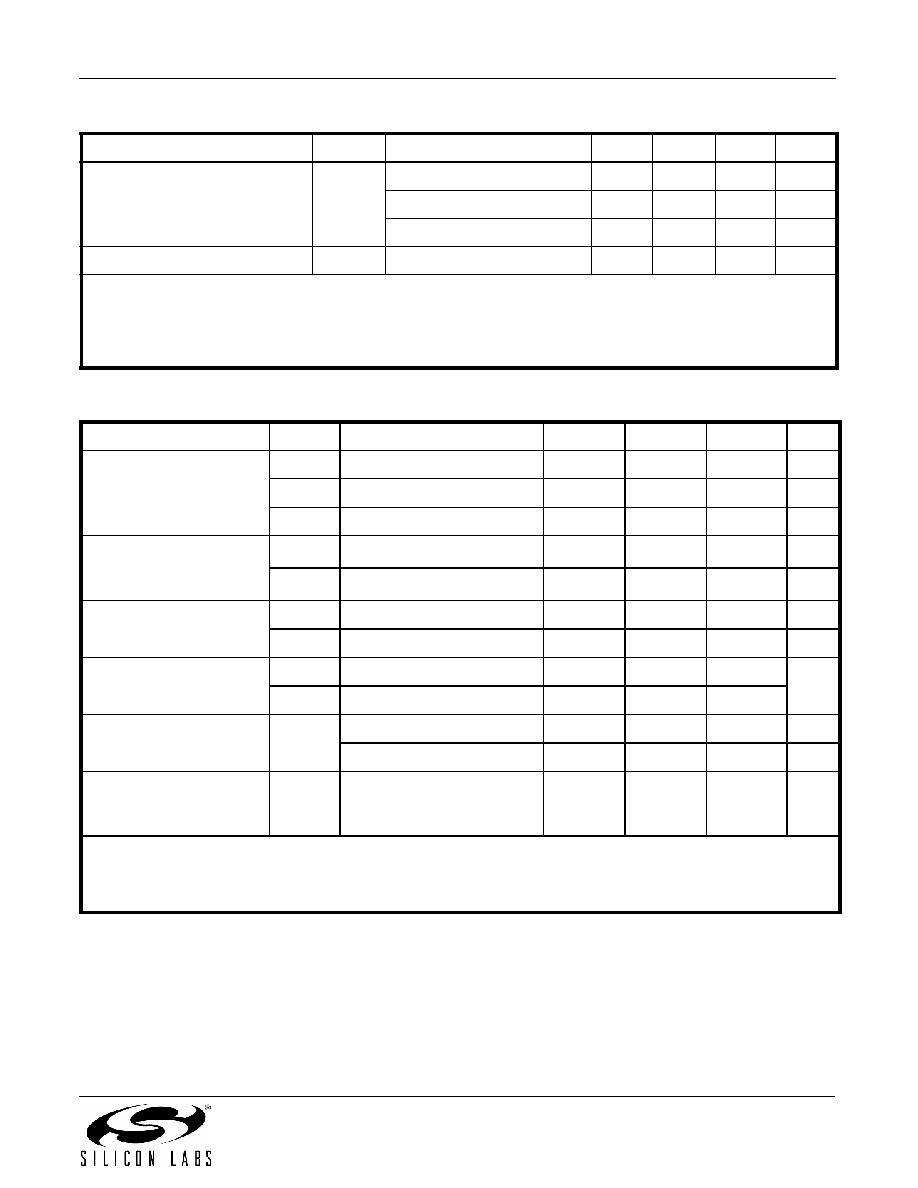

Table 3. CLK± Output Levels and Symmetry

Parameter

Symbol

Test Condition

Min

Typ

Max

Units

LVPECL Output Option1

VO

mid-level

VDD – 1.42

—

VDD – 1.25

V

VOD

swing (diff)

1.1

—

1.9

VPP

VSE

swing (single-ended)

0.55

—

0.95

VPP

LVDS Output Option2

VO

mid-level

1.125

1.20

1.275

V

VOD

swing (diff)

0.5

0.7

0.9

VPP

CML Output Option2

VO

mid-level

—

VDD – 0.75

—

V

VOD

swing (diff)

0.70

0.95

1.20

VPP

CMOS Output Option3

VOH

IOH =32mA

0.8 x VDD

—

VDD

V

VOL

IOL =32mA

—

0.4

Rise/Fall time (20/80%)

tR, tF

LVPECL/LVDS/CML

—

350

ps

CMOS with CL =15pF

—

1

—

ns

Symmetry (duty cycle)

SYM

LVPECL:

VDD – 1.3 V (diff)

LVDS:

1.25 V (diff)

CMOS:

VDD/2

45

—

55

%

Notes:

1. 50

to VDD – 2.0 V.

2. Rterm = 100 (differential).

3. CL = 15 pF

Table 2. CLK± Output Frequency Characteristics (Continued)

Parameter

Symbol

Test Condition

Min

Typ

Max

Units

Notes:

1. See Section 3. "Ordering Information" on page 7 for further details.

2. Specified at time of order by part number. Also available in frequencies from 970 to 1134 MHz and 1213 to 1417 MHz.

3. Selectable parameter specified by part number.

4. Time from powerup or tristate mode to fO.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 531AA826M000DGR | CRYSTAL OSCILLATOR, CLOCK, 826 MHz, LVPECL OUTPUT |

| 530DA21M0000DGR | CRYSTAL OSCILLATOR, CLOCK, 21 MHz, CMOS/TTL OUTPUT |

| 530DC917M000DG | CRYSTAL OSCILLATOR, CLOCK, 917 MHz, CMOS/TTL OUTPUT |

| 530HA104M000DGR | CRYSTAL OSCILLATOR, CLOCK, 104 MHz, CMOS/TTL OUTPUT |

| 531MB506M000DG | CRYSTAL OSCILLATOR, CLOCK, 506 MHz, LVPECL OUTPUT |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 531AA933M120DG | 制造商:Silicon Laboratories Inc 功能描述:SMD CRYSTAL OSC 933.12MHZ 3.3V 6PIN - Trays |

| 531AA98M1000DG | 制造商:Silicon Laboratories Inc 功能描述:SMD CRYSTAL OSCILLATOR 98.1MHZ 3.3V 6-PIN SMD - Trays |

| 531AA98M1000DGR | 制造商:Silicon Laboratories Inc 功能描述:SMD CRYSTAL OSCILLATOR 98.1MHZ 3.3V 6-PIN SMD - Tape and Reel |

| 531AB | 制造商:Datak Corporation 功能描述: |

| 531AB000106DG | 制造商:Silicon Laboratories Inc 功能描述:OSCILLATOR - Trays |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。