- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369889 > M68HC16 (Motorola, Inc.) 16-Bit Microcontroller(16位微控制器) PDF資料下載

參數(shù)資料

| 型號: | M68HC16 |

| 廠商: | Motorola, Inc. |

| 英文描述: | 16-Bit Microcontroller(16位微控制器) |

| 中文描述: | 16位微控制器(16位微控制器) |

| 文件頁數(shù): | 7/52頁 |

| 文件大?。?/td> | 358K |

| 代理商: | M68HC16 |

第1頁第2頁第3頁第4頁第5頁第6頁當(dāng)前第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

AN1283/D

MOTOROLA

7

2.10 Interrupts

An interrupt temporarily suspends normal program execution while an interrupt service routine is being ex-

ecuted. After an interrupt has been serviced, the main program resumes as if there had been no interruption.

Maskable interrupts are recognized only when the CCR I bit is cleared. Maskable interrupts are generated

by on-chip peripheral systems, and are enabled by control bits in MCU registers associated with these sys-

tems. Nonmaskable interrupt sources are not masked by the I bit. The three nonmaskable interrupt sources

are the illegal opcode trap, the software interrupt instruction, and the XIRQ pin. Operation of the XIRQ pin

is enabled by the CCR X bit.

Upon reset, both the X bit and the I bit are set, which inhibits both maskable interrupts and XIRQ interrupts.

After reset, software can clear both X and I to enable interrupt recognition. Once cleared, the X bit cannot

be set by software.

An interrupt request can be recognized at any time, but the CPU does not respond to a request until com-

pletion of the instruction being executed. Interrupt latency varies according to the number of cycles required

to complete the current instruction.

When the CPU begins to service an interrupt, the contents of the CPU registers are pushed onto the stack

in the order shown in

Table 4

.

After the CCR value is stacked, the appropriate mask bit is set to inhibit further interrupts. When an I-bit-

related interrupt occurs, the I bit is set after stacking, but the X bit is not affected. When an X-bit-related

interrupt occurs, both the X and I bits are set after stacking.

After stacking and masking take place, the priority of pending requests is evaluated, and the interrupt vector

for the highest priority pending source is fetched. Execution of the interrupt service routine begins at the

address pointed to by the vector. At the end of the interrupt service routine, the return from interrupt instruc-

tion (RTI) is executed and the stacked registers are restored from the stack (restoring the CCR restores the

X and I bits to their pre-interrupt request state), and normal program execution resumes.

2.11 Reset and Interrupt Priority

Resets and interrupts have a hardware priority that determines which reset or interrupt is serviced first when

simultaneous requests occur. There are six nonmaskable reset and interrupt sources. The priority hierarchy

for these sources is as follows:

1. POR or RESET pin

2. Clock monitor reset

3. COP watchdog reset

4. XIRQ interrupt

5. Illegal opcode interrupt

6. Software interrupt (SWI)

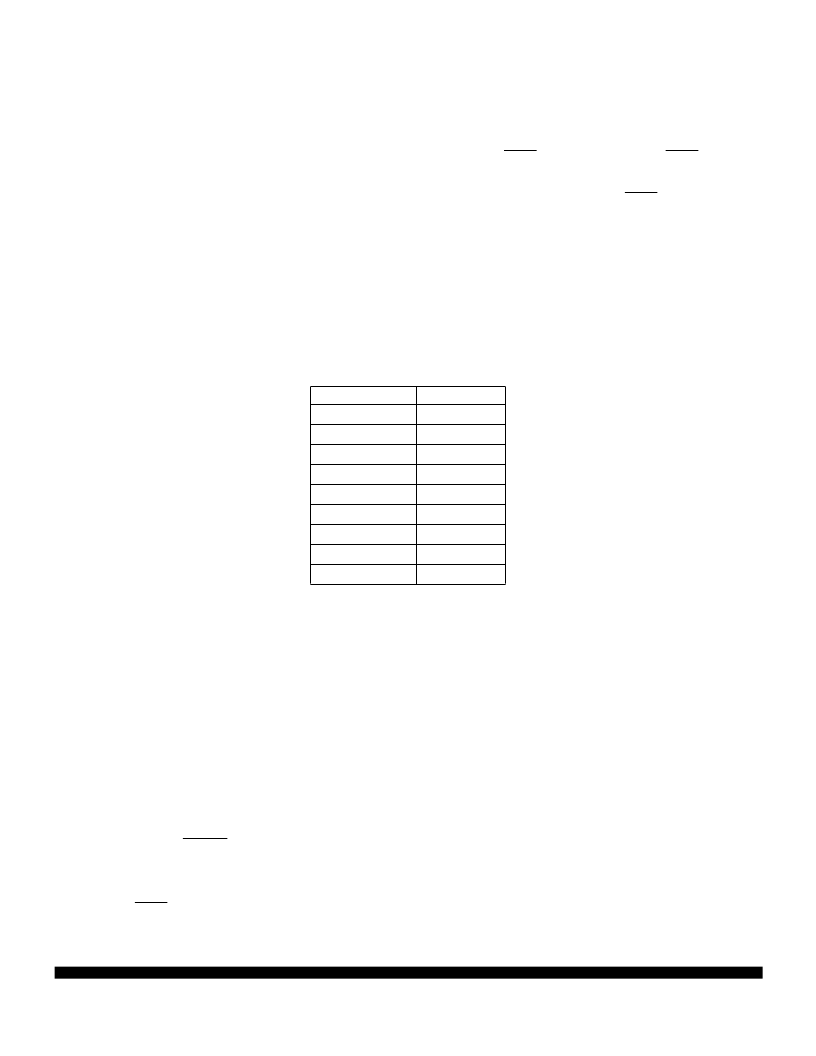

Table 4 Stacking Order on Entry to Interrupts

Memory Location CPU Registers

SP

SP – 1

SP – 2

SP – 3

SP – 4

SP – 5

SP – 6

SP – 7

SP – 8

PCL

PCH

IYL

IYH

IXL

IXH

ACCA

ACCB

CCR

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MAC08BT1 | TRIAC 0.8 AMPERE RMS 200 thru 600 Volts |

| MAC08MT1 | SENSITIVE GATE TRIACS |

| MAC08DT1 | TRIAC 0.8 AMPERE RMS 200 thru 600 Volts |

| MAC08MT1 | TRIAC 0.8 AMPERE RMS 200 thru 600 Volts |

| MAC12 | TRIACS 12 AMPERES RMS 400 thru 800 VOLTS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M68HC16Y1CFC | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:16-Bit Modular Microcontroller |

| M68HC705UGANG | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:High-density complementary metal oxide semiconductor (HCMOS) microcontroller unit |

| M68HC705UPGMR | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:High-density complementary metal oxide semiconductor (HCMOS) microcontroller unit |

| M68HC705X16PGMR | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| M68HC711CFD | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:CONFIG REGISTER PROGRAMMING FOR EEPROM-BASED MHC MICROCONTROLLERS |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。