- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369889 > M68HC16 (Motorola, Inc.) 16-Bit Microcontroller(16位微控制器) PDF資料下載

參數(shù)資料

| 型號: | M68HC16 |

| 廠商: | Motorola, Inc. |

| 英文描述: | 16-Bit Microcontroller(16位微控制器) |

| 中文描述: | 16位微控制器(16位微控制器) |

| 文件頁數(shù): | 2/52頁 |

| 文件大小: | 358K |

| 代理商: | M68HC16 |

第1頁當(dāng)前第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

MOTOROLA

2

AN1283/D

2.1.1 Accumulators

The M68HC11 CPU has two general-purpose 8-bit accumulators (A and B). Accumulators A and B can be

concatenated into a general-purpose 16-bit double accumulator (D). Although most operations can use A

or B interchangeably, the following exceptions apply:

The ABX and ABY instructions add the contents of B to the contents of IX or IY, but there are no equiv-

alent instructions that use A rather than B.

The TAP and TPA instructions transfer data from A to the CCR, or from the CCR to A, but there are

no equivalent instructions that use B rather than A.

The DAA instruction is used to adjust the content of A after BCD arithmetic operations, but there is no

equivalent instruction for B.

Add, subtract, and compare instructions that operate on both A and B (ABA, SBA, and CBA) only op-

erate in one direction, making it important to place an operand in the correct accumulator.

2.1.2 Index Registers

The M68HC11 CPU has two 16-bit index registers (IX and IY). When an indexed addressing mode is used,

a 16-bit value contained in an index register is added to an 8-bit offset provided by an instruction to create

an effective address. The index registers can also be used as counters or as temporary storage registers.

Because of M68HC11 opcode mapping, most instructions that use IY require an extra byte of machine code

and an extra cycle of execution time.

2.1.3 Stack Pointer

The M68HC11 CPU stack pointer (SP) is 16 bits wide. The stack can be located anywhere in address space

and can be any size up to the amount of memory available in the system. Stack entries are byte-width. The

SP contains the 16-bit address of the next free location in the stack, rather than the address of the latest

stack entry. SP is decremented each time data is pushed on the stack, and incremented each time data is

pulled from the stack. The stack grows downward from high to low memory as it is filled.

2.1.4 Program Counter

The 16-bit program counter (PC) contains the address of the next instruction to be executed. The PC can

be initialized with one of six possible vectors, depending on operating mode and the cause of reset.

2.1.5 Condition Code Register

As

rupt masking bits (I and X), and a stop disable bit (S). In the M68HC11 CPU, condition codes are automat-

ically updated by most instructions. However, pushes, pulls, Add B to X (ABX), Add B to Y (ABY), and

transfer/exchange instructions do not affect the condition codes.

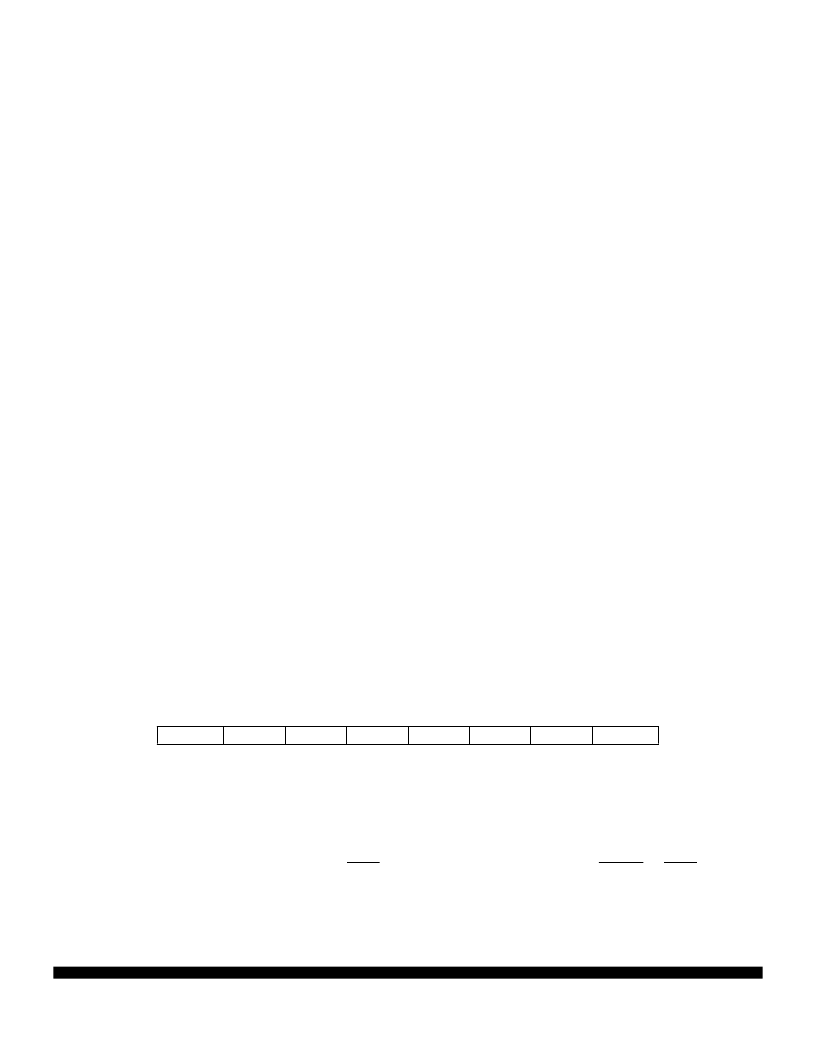

Figure 2

shows, this 8-bit register contains five condition code indicators (H, N, Z, V and C), two inter-

Figure 2 M68HC11 CPU Condition Code Register

S — STOP Enable

0 = Stop clock when STOP instruction is executed.

1 = Perform NOP when STOP instruction is executed.

X — X Interrupt Mask

Setting X disables interrupts from the XIRQ pin. X can be set only by hardware RESET or XIRQ ac-

knowledge. X can be cleared by a TAP instruction or by an RTI (when bit 6 of the value restored from

the stack to the CCR is cleared).

H — Half Carry Flag

Set when a carry from A3 or B3 occurs during BCD addition.

7

S

6

X

5

H

4

I

3

N

2

Z

1

V

0

C

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MAC08BT1 | TRIAC 0.8 AMPERE RMS 200 thru 600 Volts |

| MAC08MT1 | SENSITIVE GATE TRIACS |

| MAC08DT1 | TRIAC 0.8 AMPERE RMS 200 thru 600 Volts |

| MAC08MT1 | TRIAC 0.8 AMPERE RMS 200 thru 600 Volts |

| MAC12 | TRIACS 12 AMPERES RMS 400 thru 800 VOLTS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M68HC16Y1CFC | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:16-Bit Modular Microcontroller |

| M68HC705UGANG | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:High-density complementary metal oxide semiconductor (HCMOS) microcontroller unit |

| M68HC705UPGMR | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:High-density complementary metal oxide semiconductor (HCMOS) microcontroller unit |

| M68HC705X16PGMR | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| M68HC711CFD | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:CONFIG REGISTER PROGRAMMING FOR EEPROM-BASED MHC MICROCONTROLLERS |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。