- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369889 > M68HC16 (Motorola, Inc.) 16-Bit Microcontroller(16位微控制器) PDF資料下載

參數(shù)資料

| 型號(hào): | M68HC16 |

| 廠商: | Motorola, Inc. |

| 英文描述: | 16-Bit Microcontroller(16位微控制器) |

| 中文描述: | 16位微控制器(16位微控制器) |

| 文件頁數(shù): | 3/52頁 |

| 文件大小: | 358K |

| 代理商: | M68HC16 |

第1頁第2頁當(dāng)前第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

AN1283/D

MOTOROLA

3

I — Interrupt Mask

I is a global mask that disables maskable interrupt sources. While I is set, no maskable interrupts are

processed. After reset, I is set and can only be cleared by software. I is normally cleared when CCR

content is restored by the RTI instruction at the end of an interrupt service routine.

N — Negative Flag

Set when the MSB of a result register is set.

Z — Zero Flag

Set when all bits of a result register are zero.

V — Overflow Flag

Set when two's complement overflow occurs as the result of an operation.

C — Carry Flag

Set when carry or borrow occurs during arithmetic operation. Also used during shift and rotate

2.2 Memory Management

All M68HC11 devices have a contiguous 64 Kbyte address space that is accessed by means of a 16-line

address bus. Some devices have the upper eight address lines multiplexed with the data bus lines, while

others have non-multiplexed address and data buses. Some variants also have address extension capabil-

ities — the CPU address space remains 64 Kbytes, but on-chip logic and extra address lines are provided

to implement bank-switching in external memory. Extended memory is accessed by means of two windows

of a pre-defined size and extend.

2.3 Data Types

The M68HC11 CPU supports the following data types:

Bit data

8-bit and 16-bit signed and unsigned integers

16-bit unsigned fractions

16-bit addresses

A byte is eight bits wide and can be accessed at any byte location. A word is composed of two consecutive

bytes with the most significant byte at the lower value address. Because the M68HC11 CPU is an 8-bit CPU,

there are no special requirements for alignment of instructions or operands.

2.4 Addressing Modes

The M68HC11 CPU uses six basic types of addressing. Each type consists of one or more addressing

modes. All modes except inherent mode use an effective address. The effective address is the memory ad-

dress from which an argument is fetched or stored, or the address from which execution is to proceed. An

effective address can be specified within an instruction, or it can be calculated.

M68HC11 CPU addressing modes.

Table 1

shows the various

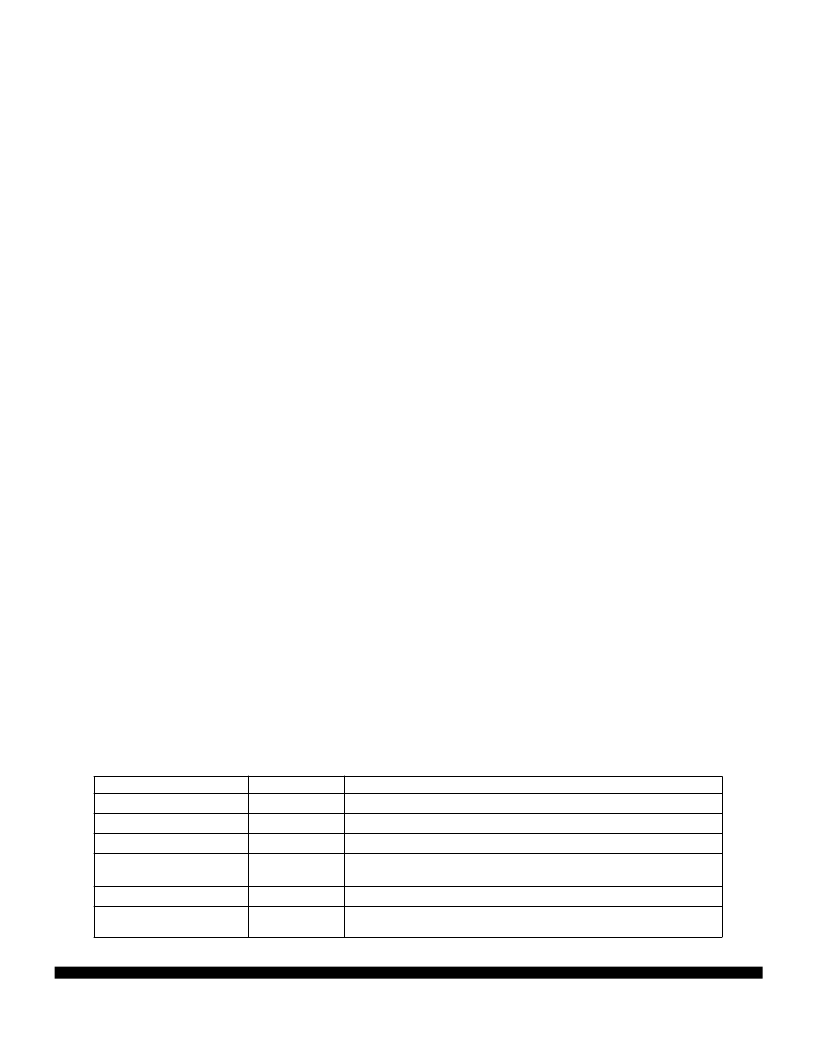

Table 1 M68HC11 CPU Addressing Modes

Mode

Direct

Extended

Immediate

Mnemonic

DIR

EXT

IMM

IND, X

IND, Y

INH

Description

Low-order byte of effective address follows opcode

Effective address follows opcode

Argument follows opcode

Effective address formed by adding unsigned 8-bit offset from instruc-

tion to index register content

Opcode contains information necessary for execution

When a branch is taken, effective address formed by adding signed 8-

bit offset from instruction to PC content.

Indexed

Inherent

Relative

REL

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MAC08BT1 | TRIAC 0.8 AMPERE RMS 200 thru 600 Volts |

| MAC08MT1 | SENSITIVE GATE TRIACS |

| MAC08DT1 | TRIAC 0.8 AMPERE RMS 200 thru 600 Volts |

| MAC08MT1 | TRIAC 0.8 AMPERE RMS 200 thru 600 Volts |

| MAC12 | TRIACS 12 AMPERES RMS 400 thru 800 VOLTS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M68HC16Y1CFC | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:16-Bit Modular Microcontroller |

| M68HC705UGANG | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:High-density complementary metal oxide semiconductor (HCMOS) microcontroller unit |

| M68HC705UPGMR | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:High-density complementary metal oxide semiconductor (HCMOS) microcontroller unit |

| M68HC705X16PGMR | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| M68HC711CFD | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:CONFIG REGISTER PROGRAMMING FOR EEPROM-BASED MHC MICROCONTROLLERS |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。