- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369889 > M68HC16 (Motorola, Inc.) 16-Bit Microcontroller(16位微控制器) PDF資料下載

參數(shù)資料

| 型號: | M68HC16 |

| 廠商: | Motorola, Inc. |

| 英文描述: | 16-Bit Microcontroller(16位微控制器) |

| 中文描述: | 16位微控制器(16位微控制器) |

| 文件頁數(shù): | 10/52頁 |

| 文件大小: | 358K |

| 代理商: | M68HC16 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁當(dāng)前第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

MOTOROLA

10

AN1283/D

IX and IY can perform the same operations as M68HC11 CPU registers of the same names, but the CPU16

instruction set provides additional indexed operations.

IZ can perform the same operations as IX and IY, and also provides an additional indexed addressing ca-

pability that replaces M68HC11 CPU direct addressing mode. Initial IZ and ZK extension field values are

included in the RESET exception vector, so that ZK : IZ can be used as a direct page pointer out of reset.

3.1.3 Stack Pointer

The CPU16 stack pointer (SP) is 16 bits wide. An associated 4-bit extension field (SK) provides 20-bit stack

addressing.

Stack implementation in the CPU16 is from high to low memory. The stack grows downward as it is filled.

SK : SP are decremented each time data is pushed on the stack, and incremented each time data is pulled

from the stack.

SK : SP point to the next available stack address, rather than to the address of the latest stack entry. Al-

though the stack pointer is normally incremented or decremented by word address, it is possible to push

and pull byte-sized data. Setting the stack pointer to an odd value causes misalignment, which affects per-

formance.

3.1.4 Program Counter

The CPU16 program counter (PC) is 16 bits wide. An associated 4-bit extension field (PK) provides 20-bit

program addressing.

CPU16 instructions are fetched from even word boundaries. PC0 always has a value of zero, to assure that

instruction fetches are made from word-aligned addresses.

3.1.5 Condition Code Register

The 16-bit condition code register can be divided into two functional blocks. The 8 MSB, which correspond

to the CCR in the M68HC11 CPU, contain the low-power stop control bit and processor status flags. The 8

LSB contain the interrupt priority field, the DSP saturation mode control bit, and the program counter ad-

dress extension field.

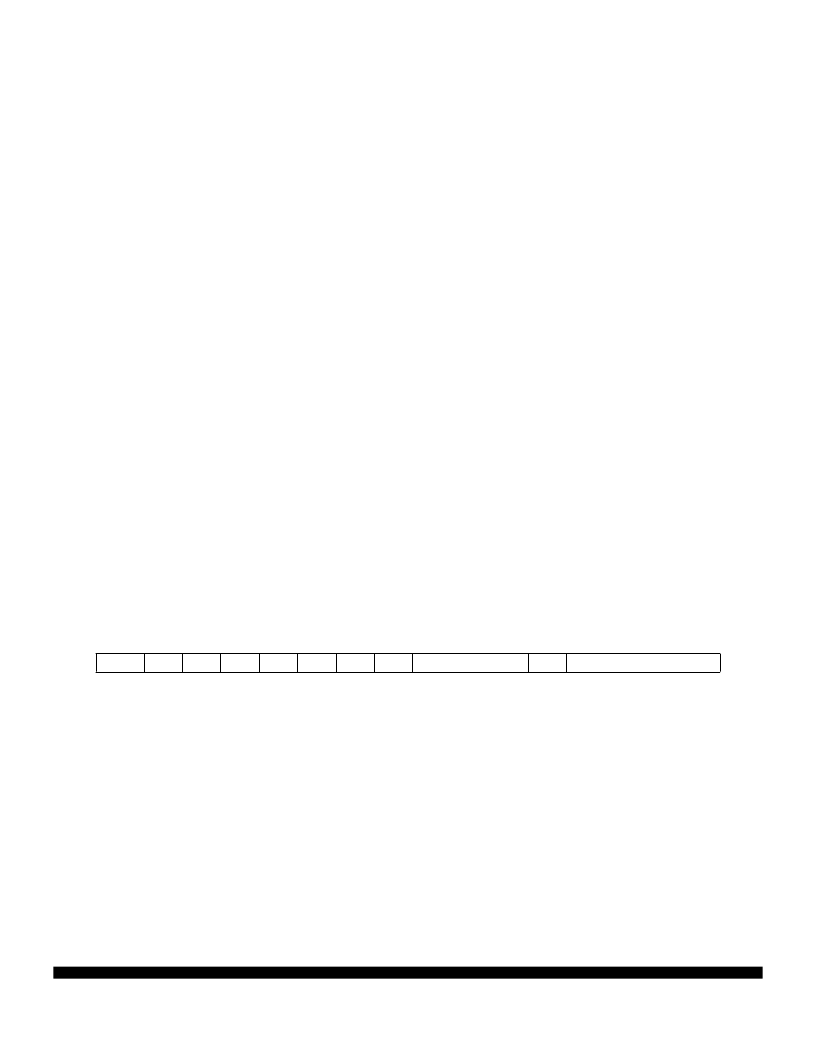

Figure 4

register follow the figure.

shows the condition code register. Detailed descriptions of each status indicator and field in the

Figure 4 CPU16 Condition Code Register

S — STOP Enable

0 = Stop clock when LPSTOP instruction is executed.

1 = Perform NOP when LPSTOP instruction is executed.

MV — Accumulator M overflow flag

Set when overflow into AM35 has occurred.

H — Half Carry Flag

Set when a carry from A3 or B3 occurs during BCD addition.

EV — Extension Bit Overflow Flag

Set when an overflow into AM31 has occurred.

N — Negative Flag

Set when the MSB of a result register is set.

Z — Zero Flag

Set when all bits of a result register are zero.

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

S

MV

H

EV

N

Z

V

C

IP

SM

PK

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MAC08BT1 | TRIAC 0.8 AMPERE RMS 200 thru 600 Volts |

| MAC08MT1 | SENSITIVE GATE TRIACS |

| MAC08DT1 | TRIAC 0.8 AMPERE RMS 200 thru 600 Volts |

| MAC08MT1 | TRIAC 0.8 AMPERE RMS 200 thru 600 Volts |

| MAC12 | TRIACS 12 AMPERES RMS 400 thru 800 VOLTS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M68HC16Y1CFC | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:16-Bit Modular Microcontroller |

| M68HC705UGANG | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:High-density complementary metal oxide semiconductor (HCMOS) microcontroller unit |

| M68HC705UPGMR | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:High-density complementary metal oxide semiconductor (HCMOS) microcontroller unit |

| M68HC705X16PGMR | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| M68HC711CFD | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:CONFIG REGISTER PROGRAMMING FOR EEPROM-BASED MHC MICROCONTROLLERS |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。