- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1924 > IDT88K8483BRI (IDT, Integrated Device Technology Inc)IC SPI-4 EXCHANGE 3PORT 672-BGA PDF資料下載

參數(shù)資料

| 型號: | IDT88K8483BRI |

| 廠商: | IDT, Integrated Device Technology Inc |

| 文件頁數(shù): | 135/162頁 |

| 文件大小: | 0K |

| 描述: | IC SPI-4 EXCHANGE 3PORT 672-BGA |

| 標(biāo)準(zhǔn)包裝: | 24 |

| 系列: | * |

| 其它名稱: | 88K8483BRI |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁當(dāng)前第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁

74 of 162

October 20, 2006

IDT IDT88K8483

Ensure that the buffer has sufficient drive capability to supply all loads. When using a buffer to drive any of the JTAG TAP pins, it may be necessary to

include an external resistor to ensure the pin is set to the correct state when the buffer is idle. Thus, TRSTB should have an external resistor to ground

when driven by an external buffer and TMS and TCK should each have an external pull-up.

GPIO

The device has 3 general purpose input/output pins. The pins’ direction is independently controlled by the DIR_OUT field in the GPIO Direction

Register (p. 145). The logical level on the pins is controlled by the LEVEL field in the GPIO Level Register (p. 146). The LEVEL field reflects the status

of any bit which is selected from the indirect access space if enabled. A bit in the indirect access space can be selected by the ADDRESS and BIT

fields in the GPIO Link Table (p. 146). A bit can be enabled by the REFLECT_EN field in the GPIO Link Table (p. 146). IDT recommends to connect all

the unused GPIO signals to an FPGA or microprocessor pins for debugging purpose.

Power Supply

The IDT88K8483 Power Supplies can be generated as shown in the design example in Figure 41 IDT88K8483 Power Supply Genera-

The IDT88K8483 system should have the following:

1. Connect the VDDA25 signals through filter to The VDDH25 / VDDL25 signals as described in Figure 42 IDT88K8483 VDDA25 Filter Circuit

2. Connected together the VDDH25 signals and the VDDL25 signals.

3. Separate the VDDC12 signals and VDDL12 signals.

4. Generate the VDDL25 / VDDH25 signals from VDDT33 signals.

5. Generate the V TT075 signals from VDDH15 signals.

Instructions

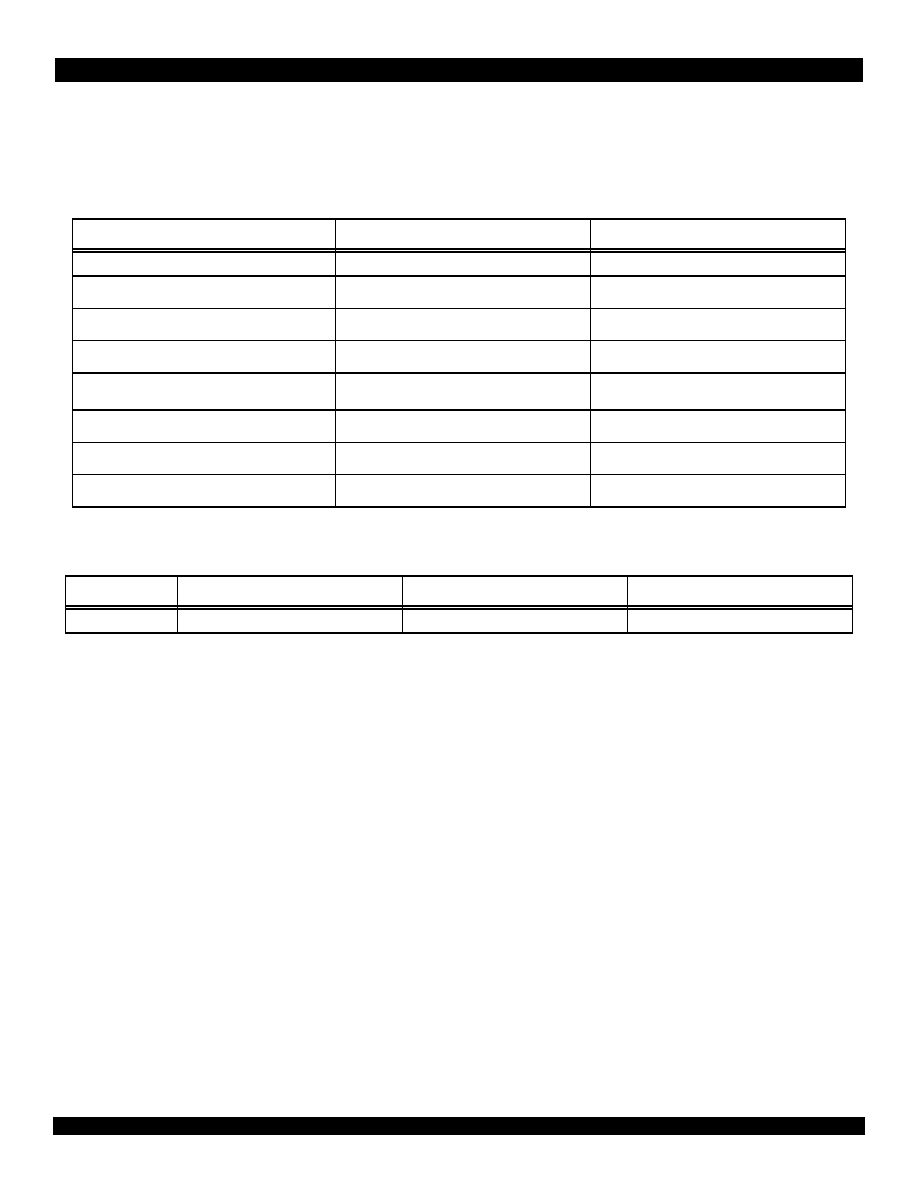

Instruction Codes

Function Description

EXTEST

000

Test the function to other devices

IDCODE

001

Used to connect the identification register

HIGHZ

100

Set outputs to Hi-Z state

CLAMP

011

Clamp the output latches

SAMPLE

010

Sample all the inputs and outputs

RUNBIST

110

BIST

USERCODE

101

User code

BYPASS

111

Used to bypass the device

Table 11 JTAG Instruction Code

Version

Part Number

Manufacture ID

Fixed

0

0x4af

0x33

1

Table 12 JTAG ID

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IDT88P8341BHI | IC SPI3-SPI4 EXCHANGE 820-PBGA |

| IDT88P8342BHI | IC SPI3-SPI4 EXCHANGE 820-PBGA |

| IDT88P8344BHI | IC SPI3-SPI4 EXCHANGE 820-PBGA |

| IDT89H24NT24G2ZBHLG | IC PCI SW 24LANE 24PORT 324BGA |

| IDT89HPES16NT2ZBBCG | IC PCI SW 16LANE 2PORT 484-CABGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT88P8341BHGI | 功能描述:IC SPI3-SPI4 EXCHANGE 820-PBGA RoHS:是 類別:集成電路 (IC) >> 專用 IC 系列:* 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:1 系列:- 類型:調(diào)幀器 應(yīng)用:數(shù)據(jù)傳輸 安裝類型:表面貼裝 封裝/外殼:400-BBGA 供應(yīng)商設(shè)備封裝:400-PBGA(27x27) 包裝:散裝 |

| IDT88P8341BHI | 功能描述:IC SPI3-SPI4 EXCHANGE 820-PBGA RoHS:否 類別:集成電路 (IC) >> 專用 IC 系列:* 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:1 系列:- 類型:調(diào)幀器 應(yīng)用:數(shù)據(jù)傳輸 安裝類型:表面貼裝 封裝/外殼:400-BBGA 供應(yīng)商設(shè)備封裝:400-PBGA(27x27) 包裝:散裝 |

| IDT88P8342BHGI | 功能描述:IC SPI3-SPI4 EXCHANGE 820-PBGA RoHS:是 類別:集成電路 (IC) >> 專用 IC 系列:* 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:1 系列:- 類型:調(diào)幀器 應(yīng)用:數(shù)據(jù)傳輸 安裝類型:表面貼裝 封裝/外殼:400-BBGA 供應(yīng)商設(shè)備封裝:400-PBGA(27x27) 包裝:散裝 |

| IDT88P8342BHI | 功能描述:IC SPI3-SPI4 EXCHANGE 820-PBGA RoHS:否 類別:集成電路 (IC) >> 專用 IC 系列:* 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:1 系列:- 類型:調(diào)幀器 應(yīng)用:數(shù)據(jù)傳輸 安裝類型:表面貼裝 封裝/外殼:400-BBGA 供應(yīng)商設(shè)備封裝:400-PBGA(27x27) 包裝:散裝 |

| IDT88P8344 | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:SPI EXCHANGE 4 x SPI-3 TO SPI-4 Issue 1.0 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。