- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1924 > IDT88K8483BRI (IDT, Integrated Device Technology Inc)IC SPI-4 EXCHANGE 3PORT 672-BGA PDF資料下載

參數(shù)資料

| 型號(hào): | IDT88K8483BRI |

| 廠商: | IDT, Integrated Device Technology Inc |

| 文件頁數(shù): | 105/162頁 |

| 文件大小: | 0K |

| 描述: | IC SPI-4 EXCHANGE 3PORT 672-BGA |

| 標(biāo)準(zhǔn)包裝: | 24 |

| 系列: | * |

| 其它名稱: | 88K8483BRI |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁當(dāng)前第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁

47 of 162

October 20, 2006

IDT IDT88K8483

Egress associated status channel

Bit alignment

The alignment selection is programed by AUTO_ALIGN flag in the SPI-4 Egress Automatic Alignment Control Register (p. 115).

The device is responsible for edge transition histogram for each lane. The data is sampled by 10-phased shifted clock during each clock cycle.

Each consecutive pairs of sampled values are XORed and accumulated during a fixed observation window to generate transition edge histogram.

The measure histogram is triggered by writing to the LANE field in the SPI-4 Histogram Measure Launch Register (p. 117). The measurement

process is indicated by a BUSY flag in the SPI-4 Histogram Measure Status Register (p. 117). The BUSY field is set to 1 when a measurement is

launched. The BUSY field is auto cleared to 0 when the measurement is finished. The status channel TAP is configured by the AUTO_ALIGN field in

The bit alignment sequence is as follows:

- Write lane number in the LANE field in the SPI-4 Histogram Measure Launch Register (p. 117).

- Poll the BUSY field in the SPI-4 Histogram Measure Status Register (p. 117). If BUSY is 0, then read the C[n] field in the SPI-4 Histogram Counter

Register (p. 117) which indicates the counter value. The counter value is used to select the tap.

- Write the selected Tap value to TAP field in the SPI-4 Bit Alignment Result Register (p. 118).

De-skew

The De-skew block can de-skew +/-1bit. For diagnostic purpose, an out of range offset between lines is provided. If deskew is more than 2 bits,

then the E_DSK_OOR field in the SPI-4 Egress Status Register (p. 115) is set. E_DSK_OOR field is cleared when in range.

Status Termination

The protocol (LVDS/LVTTL) is configured by SPI4_LVDSSTA input pin. The status channel has 2 states, IN_SYNCH and OUT_OF_SYNCH. A

number of consecutive DIP-2 error-free values cause a transition from OUT_OF_SYNCH to IN_SYNCH state. This number is configured by SPI-4

Egress Configuration Register (p. 113). A number of consecutive DIP-2 errors will force the machine to OUT_OF_SYNCH state. This number is

configured in the SPI-4 Egress Configuration Register (p. 113). In LVDS protocol mode, 12 consecutive “11” will force the machine to

OUT_OF_SYNCH state. In LVTTL protocol mode, 12 consecutive ‘11’ will force the machine to OUT_OF_SYNCH state. The machine’s state is indi-

cated by E_SYNCV field in the SPI-4 Egress Status Register (p. 115). Any transition on the E_SYNCV field is captured, and generates an interrupt if

enabled.

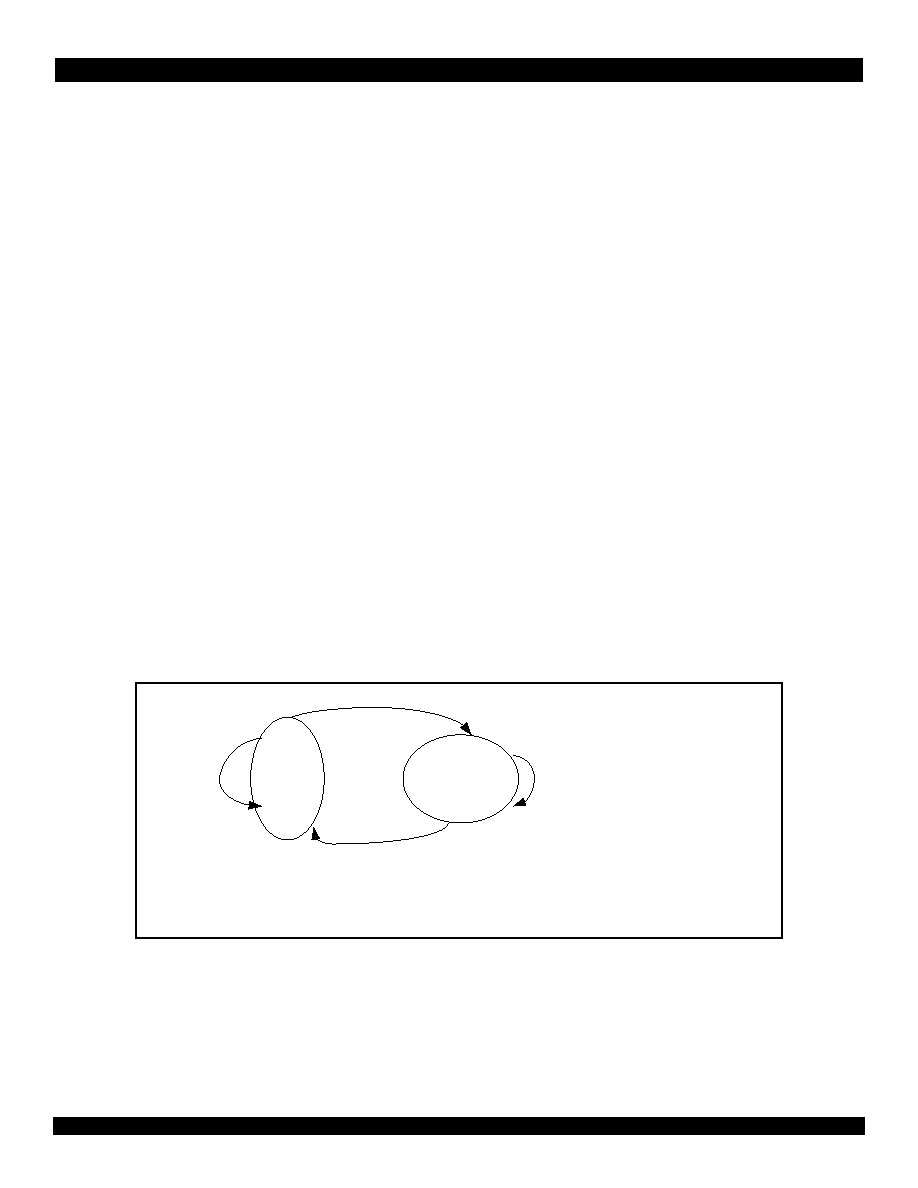

Figure 19 Status Channel State Machine

The device supports one or two sets of calendars. If E_CSW_EN field in the SPI-4 Egress Calendar Switch Control Register (p. 116) is set to 1,

then two sets of calendars mode are used. In this case, a calendar selection word must be placed following the framing bit.

If CAL_SEL field in the SPI-4 Egress Calendar Switch Control Register (p. 116) is cleared to 0, then the device selects calendar 0, and the selec-

tion word is fixed to 01b. If CAL_SEL field is set to 1, then the device selects calendar 1, and the selection word is fixed to 10b.

IN_SYNCH

A

A=a number consecutive DIP-2 error free

B=a number of consecutive DIP-2 error,training, port disabled or

reset

Out of

synch

B

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IDT88P8341BHI | IC SPI3-SPI4 EXCHANGE 820-PBGA |

| IDT88P8342BHI | IC SPI3-SPI4 EXCHANGE 820-PBGA |

| IDT88P8344BHI | IC SPI3-SPI4 EXCHANGE 820-PBGA |

| IDT89H24NT24G2ZBHLG | IC PCI SW 24LANE 24PORT 324BGA |

| IDT89HPES16NT2ZBBCG | IC PCI SW 16LANE 2PORT 484-CABGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT88P8341BHGI | 功能描述:IC SPI3-SPI4 EXCHANGE 820-PBGA RoHS:是 類別:集成電路 (IC) >> 專用 IC 系列:* 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:1 系列:- 類型:調(diào)幀器 應(yīng)用:數(shù)據(jù)傳輸 安裝類型:表面貼裝 封裝/外殼:400-BBGA 供應(yīng)商設(shè)備封裝:400-PBGA(27x27) 包裝:散裝 |

| IDT88P8341BHI | 功能描述:IC SPI3-SPI4 EXCHANGE 820-PBGA RoHS:否 類別:集成電路 (IC) >> 專用 IC 系列:* 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:1 系列:- 類型:調(diào)幀器 應(yīng)用:數(shù)據(jù)傳輸 安裝類型:表面貼裝 封裝/外殼:400-BBGA 供應(yīng)商設(shè)備封裝:400-PBGA(27x27) 包裝:散裝 |

| IDT88P8342BHGI | 功能描述:IC SPI3-SPI4 EXCHANGE 820-PBGA RoHS:是 類別:集成電路 (IC) >> 專用 IC 系列:* 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:1 系列:- 類型:調(diào)幀器 應(yīng)用:數(shù)據(jù)傳輸 安裝類型:表面貼裝 封裝/外殼:400-BBGA 供應(yīng)商設(shè)備封裝:400-PBGA(27x27) 包裝:散裝 |

| IDT88P8342BHI | 功能描述:IC SPI3-SPI4 EXCHANGE 820-PBGA RoHS:否 類別:集成電路 (IC) >> 專用 IC 系列:* 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:1 系列:- 類型:調(diào)幀器 應(yīng)用:數(shù)據(jù)傳輸 安裝類型:表面貼裝 封裝/外殼:400-BBGA 供應(yīng)商設(shè)備封裝:400-PBGA(27x27) 包裝:散裝 |

| IDT88P8344 | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:SPI EXCHANGE 4 x SPI-3 TO SPI-4 Issue 1.0 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。