- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄1924 > IDT88K8483BRI (IDT, Integrated Device Technology Inc)IC SPI-4 EXCHANGE 3PORT 672-BGA PDF資料下載

參數(shù)資料

| 型號(hào): | IDT88K8483BRI |

| 廠商: | IDT, Integrated Device Technology Inc |

| 文件頁(yè)數(shù): | 116/162頁(yè) |

| 文件大小: | 0K |

| 描述: | IC SPI-4 EXCHANGE 3PORT 672-BGA |

| 標(biāo)準(zhǔn)包裝: | 24 |

| 系列: | * |

| 其它名稱(chēng): | 88K8483BRI |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)當(dāng)前第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)第158頁(yè)第159頁(yè)第160頁(yè)第161頁(yè)第162頁(yè)

57 of 162

October 20, 2006

IDT IDT88K8483

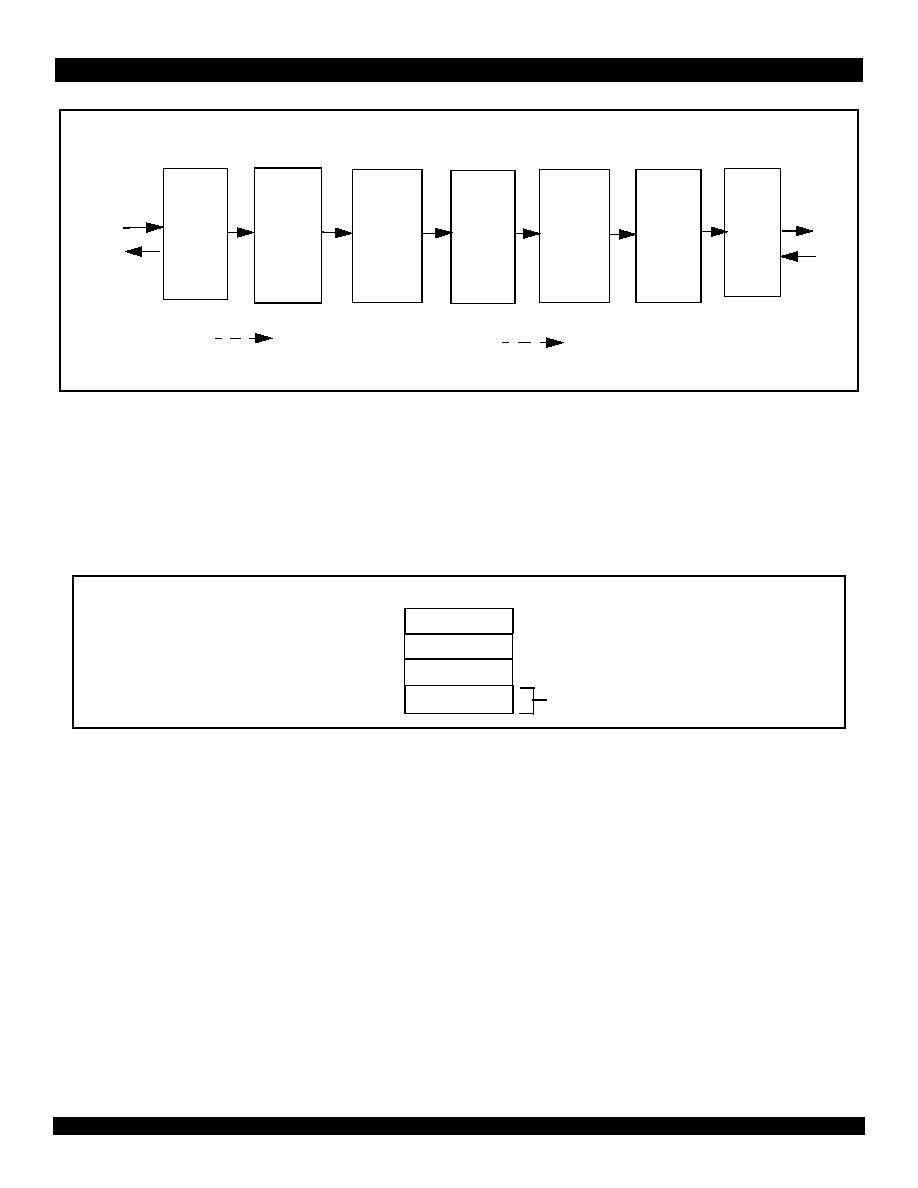

Figure 24 Flow Control Mode 1 Application Example

Flow Control Mode 2 - Buffering

In the buffering option the IDT88K8483 gets the data in interleaved mode or in packet mode and it sends the data in packet mode or in interleave

mode. In this option, the EBC[2:0] field in the (p. 129) should be configured to the number of FIFOs in the QDR-II (64, 32, 16, 8 or 4) as described in

. Each FIFO gets the same amount of buffer size.

Figure 25 QDR-II FIFOs Allocation Example For Buffering Option

In buffering option, the PFP and the QDR-II should be programed to packet mode by setting to 1 the PKT_MODE field in the PFP Egress Packet

Mode Control Registers (p. 123) and the PKT_MODE field in the Auxiliary Packet Mode Configuration Register (p. 131). In addition, the EBP_THR

field in the Auxiliary Early Backpressure Threshold Register (p. 131) should be programmed with the early back-pressure threshold value. Also, the

flow control mode 2 should be enabled in the PFP by setting to 1 the EBP_EN field in the PFP Egress Packet Mode Control Registers (p. 123). The

device fixes the Second Free Segments (Second Free Segments) to 6 as shown in Figure 26 QDR-II Flow Control Example For Buffering

There are three status options per FIFO in the QDR-II: starving hungry and satisfied. In the QDR-II for LP0 (for example), in normal operation there

are enough free segments, so the FIFO status is starving, and the QDR-II is sending starving status to the PFP. When the number of free segments is

less than EBP_THR (for example 100 segments), the QDR-II FIFO status is changed to hungry, and the QDR-II starts sending hungry status to the

PFP. When the number of free segments is less than the Second Free Segments (6 segments), the QDR-II FIFO status is changed to satisfied, and

the QDR-II starts sending satisfied status to the PFP.

SPI-4

Ingress

Port

Buffer

SPI-4

Egress

Port

Buffer

PFP

Ingress

SPI-4

Ingress

Interface

SPI-4

Egress

Interface

QDR

PFP

Egress

Framer

NP

508 segments

127K bytes

508 segments

127K bytes

8K segments

2M bytes

Reassembly

Interleaved

Channels

Non-Interleaved

Channels

data

status

data

status

LID 63

LID 1

LID 0

QDR-II (8K segments, 2M bytes, 16M bits)

...

128 segments / 32K bytes

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IDT88P8341BHI | IC SPI3-SPI4 EXCHANGE 820-PBGA |

| IDT88P8342BHI | IC SPI3-SPI4 EXCHANGE 820-PBGA |

| IDT88P8344BHI | IC SPI3-SPI4 EXCHANGE 820-PBGA |

| IDT89H24NT24G2ZBHLG | IC PCI SW 24LANE 24PORT 324BGA |

| IDT89HPES16NT2ZBBCG | IC PCI SW 16LANE 2PORT 484-CABGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT88P8341BHGI | 功能描述:IC SPI3-SPI4 EXCHANGE 820-PBGA RoHS:是 類(lèi)別:集成電路 (IC) >> 專(zhuān)用 IC 系列:* 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:1 系列:- 類(lèi)型:調(diào)幀器 應(yīng)用:數(shù)據(jù)傳輸 安裝類(lèi)型:表面貼裝 封裝/外殼:400-BBGA 供應(yīng)商設(shè)備封裝:400-PBGA(27x27) 包裝:散裝 |

| IDT88P8341BHI | 功能描述:IC SPI3-SPI4 EXCHANGE 820-PBGA RoHS:否 類(lèi)別:集成電路 (IC) >> 專(zhuān)用 IC 系列:* 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:1 系列:- 類(lèi)型:調(diào)幀器 應(yīng)用:數(shù)據(jù)傳輸 安裝類(lèi)型:表面貼裝 封裝/外殼:400-BBGA 供應(yīng)商設(shè)備封裝:400-PBGA(27x27) 包裝:散裝 |

| IDT88P8342BHGI | 功能描述:IC SPI3-SPI4 EXCHANGE 820-PBGA RoHS:是 類(lèi)別:集成電路 (IC) >> 專(zhuān)用 IC 系列:* 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:1 系列:- 類(lèi)型:調(diào)幀器 應(yīng)用:數(shù)據(jù)傳輸 安裝類(lèi)型:表面貼裝 封裝/外殼:400-BBGA 供應(yīng)商設(shè)備封裝:400-PBGA(27x27) 包裝:散裝 |

| IDT88P8342BHI | 功能描述:IC SPI3-SPI4 EXCHANGE 820-PBGA RoHS:否 類(lèi)別:集成電路 (IC) >> 專(zhuān)用 IC 系列:* 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:1 系列:- 類(lèi)型:調(diào)幀器 應(yīng)用:數(shù)據(jù)傳輸 安裝類(lèi)型:表面貼裝 封裝/外殼:400-BBGA 供應(yīng)商設(shè)備封裝:400-PBGA(27x27) 包裝:散裝 |

| IDT88P8344 | 制造商:IDT 制造商全稱(chēng):Integrated Device Technology 功能描述:SPI EXCHANGE 4 x SPI-3 TO SPI-4 Issue 1.0 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。