- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370008 > PM2329 Telecommunication IC PDF資料下載

參數(shù)資料

| 型號: | PM2329 |

| 英文描述: | Telecommunication IC |

| 中文描述: | 通信集成電路 |

| 文件頁數(shù): | 94/162頁 |

| 文件大?。?/td> | 1581K |

| 代理商: | PM2329 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁當(dāng)前第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁

Proprietary and Confidential to PMC-Sierra, Inc and for its Customers

’

Internal Use

Document ID: PMC-2010146, Issue 4

97

PM2329 ClassiPI Network Classification Processor Datasheet

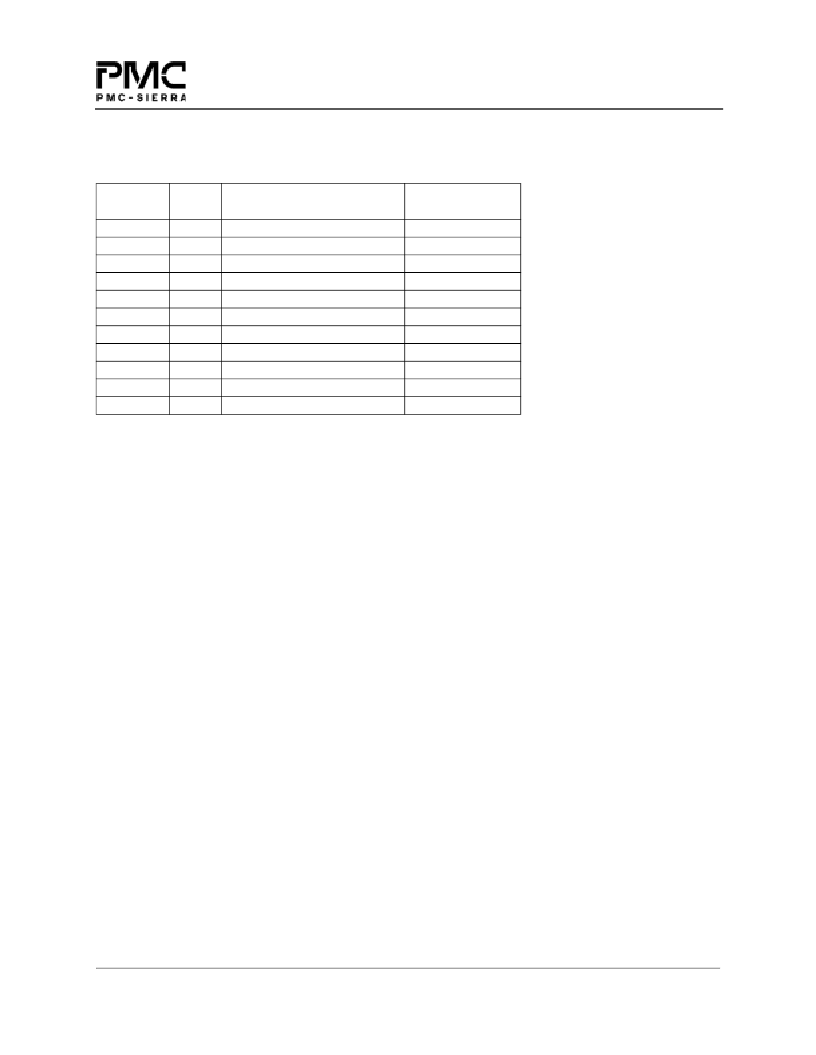

4.2.2.9 E-RAM Configuration Register (ECR; 8230h)

Access Mode: Read/Write, Global

The bits in this register are used to configure the logical E-Word. This register must be programmed before

any E-RAM accesses are performed. This register should not be updated when E-RAM operations are in

progress, normally this register will be written during initialization only. In cascade mode, global write will

configure all the devices together.

E-RAM Enable

When this bit is reset to 0, all E-RAM operations are disabled. No C-Word will be supported in this

case.

When this bit is set to 1, E-RAM operations are enabled. C-Word is always assumed to be present in this

case. D-Words are defined using the D-Word Definition fields as explained below.

D-Word Definition

If E-RAM is present, up to 7 D-Words (depending on the physical width of the E-RAM) can be

configured. These 21 bits define the D-Word type for these 7 D-Words. the PM2329 also interprets this

register to obtain the logical E-Word Width. Three bits define each of the D-Words as follows:

000

D-Word Absent

001

Packet Count

010

Byte Count

011

Timestamp/State

100

User Defined

101

(Reserved)

110

(Reserved)

111

(Reserved)

The user can force gaps in the D-Words by programming them to be user defined.

Bit

Range

63:32

31

30:28

27:25

24:22

21:19

18:16

15:13

12:10

9:3

2:0

Size

32

1

3

3

3

3

3

3

3

7

3

Name

Value after

Reset

Undefined

0

000

000

000

000

000

000

000

Undefined

00h

(Reserved)

E-RAM Enable

D-Word #0 Definition

D-Word #1 Definition

D-Word #2 Definition

D-Word #3 Definition

D-Word #4 Definition

D-Word #5 Definition

D-Word #6 Definition

(Reserved)

E-RAM Width

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PM239P | Analog Comparator |

| PM30RHC060 | TRANSISTOR | IGBT POWER MODULE | 3-PH BRIDGE | 600V V(BR)CES | 30A I(C) |

| PM3321-QC | DATA CROSS CONNECT|LDCC|84PIN|PLASTIC |

| PM355AJ | Voltage-Feedback Operational Amplifier |

| PM355AZ | Voltage-Feedback Operational Amplifier |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PM233-155.52M | 制造商:CONNOR-WINFIELD 制造商全稱:Connor-Winfield Corporation 功能描述:5.0x7.0mm Surface Mount LVPECL Clock Oscillator Series |

| PM2379-001 | 制造商:Delphi Corporation 功能描述:TAPE MARK WHT |

| PM238 | 制造商:PURDY 制造商全稱:PURDY 功能描述:AC Fans and Blowers |

| PM238-115-1751BT-4 | 制造商:INTERFAN 功能描述:Fan, AC, 115V, 172x150x51mm, Obround, 238CFM, 3100RPM, 55dBA, Terminal Block |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。