- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄366557 > AMD-K5 (Advanced Micro Devices, Inc.) 32-Bit Superior Price/Performance Value Microprocessor(32位高性/價比微處理器) PDF資料下載

參數(shù)資料

| 型號: | AMD-K5 |

| 廠商: | Advanced Micro Devices, Inc. |

| 英文描述: | 32-Bit Superior Price/Performance Value Microprocessor(32位高性/價比微處理器) |

| 中文描述: | 32位卓越的價格/性能值微處理器(32位高性/價比微處理器) |

| 文件頁數(shù): | 34/100頁 |

| 文件大小: | 2533K |

| 代理商: | AMD-K5 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁當(dāng)前第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁

24

AMD-K5 Processor Data Sheet

18522F/0—Jan1997

PRELIMINARY INFORMATION

TMS

Test Mode Select

The TMS signal is used to select the TAP Test modes. This sig-

nal is sampled on the rising edge of the TCK. TMS has an inter-

nal pull-up resistor.

Input

TRST

Test Reset

Asserting TRST initializes the TAP controller.

Input

W/R

Write/Read

The W/R signal is used with other control signals to distinguish

bus cycles and special cycles. These cycles are defined in Table

5 and Table 6 on page 27. W/R is driven active with ADS, and

floated with BOFF and bus hold.

Output

WB/WT

Writeback/Writethrough

The state of WB/WT determines the MESI cache protocol state

of a data line during cache line fills. When the signal is driven

High, the cache line will be loaded in the exclusive state. When

the signal is driven Low, the cache line will be loaded in the

shared state.

Input

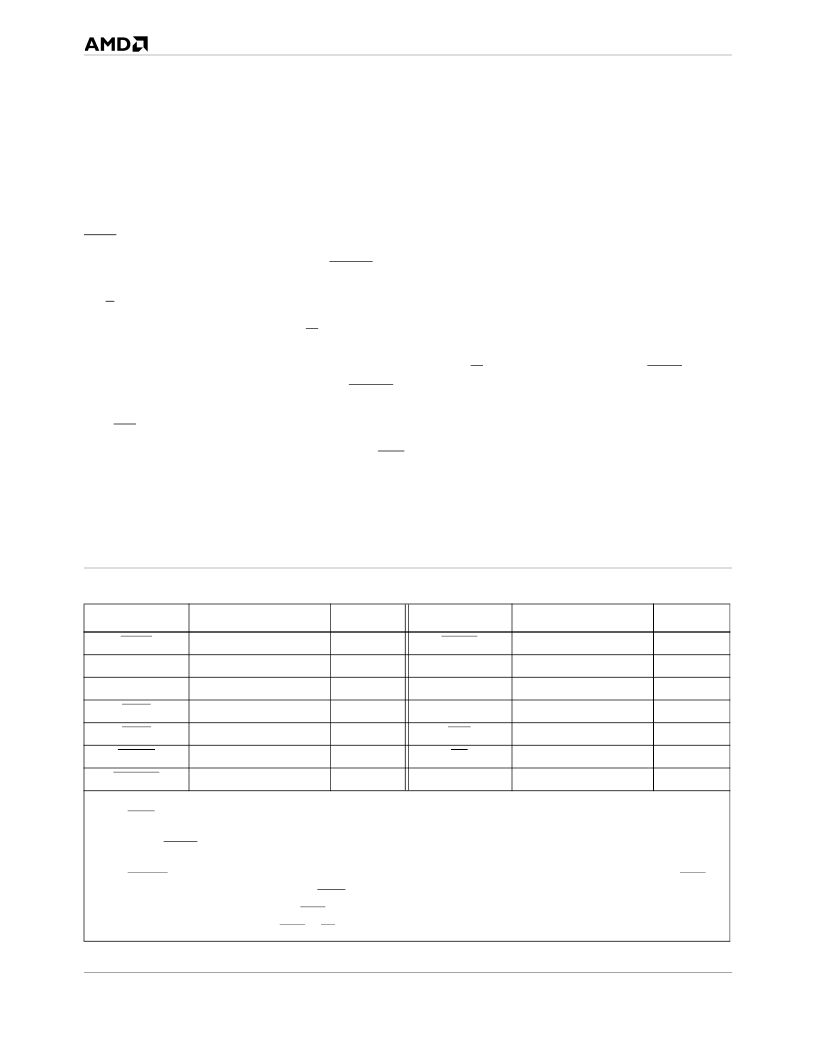

Table 1.

Input Pins

Name

A20M

AHOLD

BF

BOFF

BRDY

BRDYC

BUSCHK

Type

Note

Note 1

Name

IGNNE

INIT

INTR

INV

KEN

NA

NMI

Type

Note

Asynchronous

Synchronous

Synchronous

Synchronous

Synchronous

Synchronous

Synchronous

Asynchronous

Asynchronous

Asynchronous

Synchronous

Synchronous

Synchronous

Asynchronous

Note 2

Note 5

Note 6

Note 3

Notes:

1. A20M may change during RESET or during a serializing event like an I/O write. A state change at other times will result in incorrect

address generation on subsequent memory cycles.

2. BF and FRCMC are normally connected to V

CC

or V

SS

by a jumper. For correct operation, any change on these signals should be

followed by a RESET.

3. BUSCHK is sampled in every clock. Any asserted sample is remembered and takes effect on the same clock as the last BRDY.

4. These are sampled in the same clock as BRDY.

5. This is sampled in the same clock as EADS.

6. These are sampled with the first BRDY or NA and must meet setup to every clock

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AMD-K6-2 | 32 Bit Microprocessor With 64-Kbyte Level-one Cache High-Performance and Multimedia Execution Unit(帶64K字節(jié)緩存和高性能多媒體執(zhí)行單元的32位微處理器) |

| AMD-K6-III | 32-Bit Microprocessor Advanced RISC86 Superscalar Microarchitecture and 3D Technology(32位微處理器帶3D技術(shù)和高級的RISC86超標(biāo)量微體系結(jié)構(gòu)) |

| AMD-K6 | Circular Connector; No. of Contacts:5; Series:MS27497; Body Material:Aluminum; Connecting Termination:Crimp; Connector Shell Size:14; Circular Contact Gender:Pin; Circular Shell Style:Wall Mount Receptacle; Insert Arrangement:14-5 RoHS Compliant: No |

| AMD27C64-150PI | 64 Kilobit (8,192 x 8-Bit) CMOS EPROM |

| AMD27C64 | 64 Kilobit (8,192 x 8-Bit) CMOS EPROM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AMD-K5-PR100ABQ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:32-Bit Microprocessor |

| AMD-K5-PR120ABR | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:32-Bit Microprocessor |

| AMD-K5-PR133ABQ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:32-Bit Microprocessor |

| AMD-K5-PR133ABR | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:32-Bit Microprocessor |

| AMD-K5-PR166ABX | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:32-Bit Microprocessor |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。