- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄16537 > AD9558/PCBZ (Analog Devices Inc)BOARD EVAL FOR AD9558 PDF資料下載

參數(shù)資料

| 型號(hào): | AD9558/PCBZ |

| 廠商: | Analog Devices Inc |

| 文件頁(yè)數(shù): | 80/104頁(yè) |

| 文件大小: | 0K |

| 描述: | BOARD EVAL FOR AD9558 |

| 產(chǎn)品變化通告: | AD9558 Minor Metal Mask Change 17/Apr/2012 |

| 設(shè)計(jì)資源: | AD9558 Eval Brd BOM AD9558 Schematic |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 系列: | * |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)當(dāng)前第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)

Data Sheet

AD9558

Rev. B | Page 77 of 104

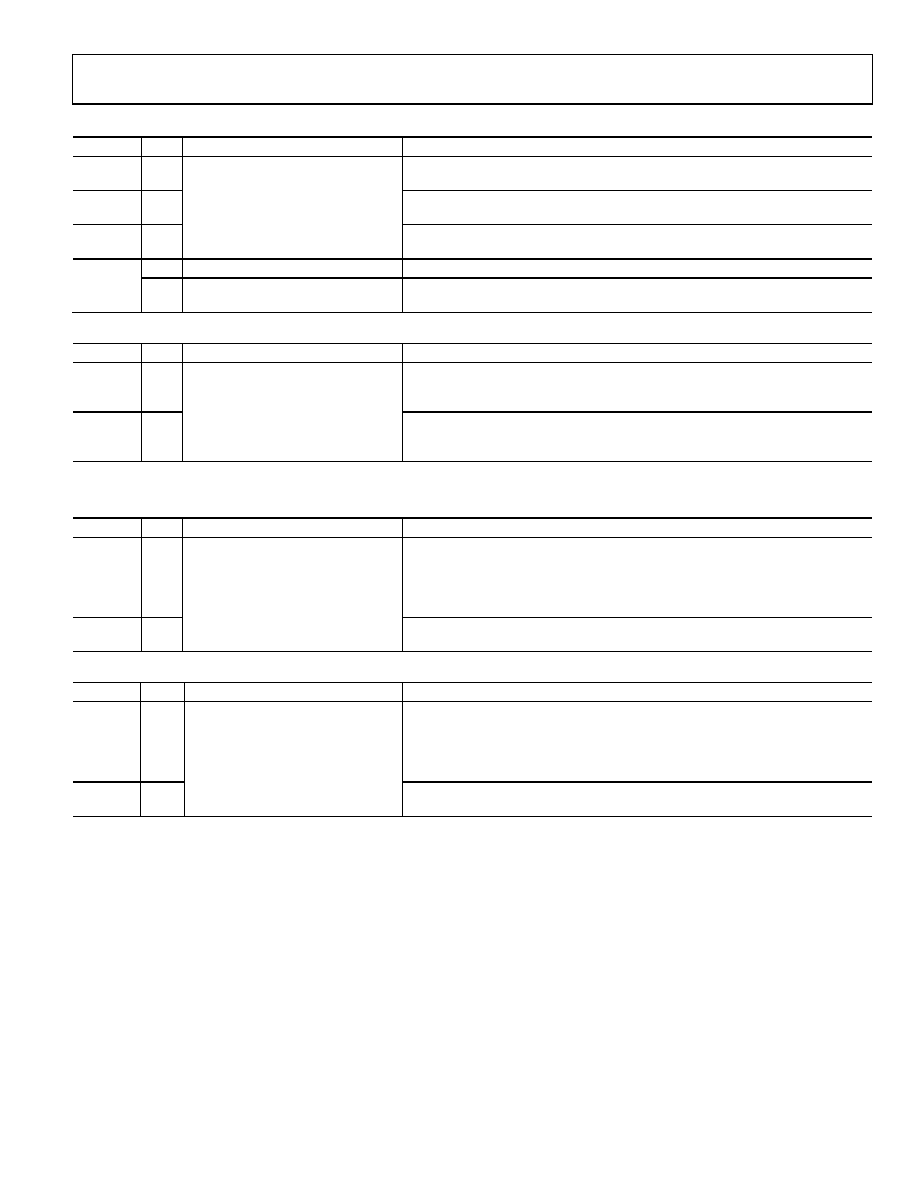

Table 57. Fixed Closed-Loop Phase Lock Offset

Address

Bits

Bit Name

Description

0x030C

[7:0]

Fixed phase lock offset (signed; ps)

Fixed phase lock offset, Bits[7:0].

Default: 0x00.

0x030D

[7:0]

Fixed phase lock offset, Bits[15:8].

Default 0x00.

0x030E

[7:0]

Fixed phase lock offset, Bits[23:16].

Default: 0x00.

0x030F

[7:6]

Reserved

Reserved; default: 0x0.

[5:0]

Fixed phase lock offset (signed; ps)

Fixed phase lock offset, Bits[29:24].

Default: 0x00.

Table 58. Incremental Closed-Loop Phase Lock Offset Step Size1

Address

Bits

Bit Name

Description

0x0310

[7:0]

Incremental phase lock offset

step size (ps)

Incremental phase lock offset step size, Bits[7:0].

Default: 0x00.

This controls the static phase offset of the DPLL while it is locked.

0x0311

[7:0]

Incremental phase lock offset step size, Bits[15:8].

Default: 0x00.

This controls the static phase offset of the DPLL while it is locked.

1

Note that the default incremental closed-loop phase lock offset step size value is 0x0000 = 0 (0 ns).

Table 59. Phase Slew Rate Limit

Address

Bits

Bit Name

Description

0x0312

[7:0]

Phase slew rate limit (s/sec)

Phase slew rate limit, Bits[7:0].

Default: 0x00.

This register controls the maximum allowable phase slewing during transients

and reference switching.

The default phase slew rate limit is 0, or disabled. Minimum useful value is 310 s/sec.

0x0313

[7:0]

Phase slew rate limit, Bits[15:8].

Default: 0x00.

Table 60. History Accumulation Timer

Address

Bits

Bit Name

Description

0x0314

[7:0]

History accumulation timer (ms)

History accumulation timer bits[7:0].

Default: 0x0A. For Register 0x0314 and Register 0x0315, 0x000A = 10 ms.

Maximum is 65 sec. This register controls the amount of tuning word averaging used

to determine the tuning word used in holdover. Never program a timer value of

zero. The default value is 0x000A = 10 decimal, which equates to 10 ms

0x0315

[7:0]

History accumulation timer bits[15:8].

Default: 0x00.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| GBM22DSAH | CONN EDGECARD 44POS R/A .156 SLD |

| DK-2632-03 | CABLE FIBER OPTIC DUAL LC-SC 3M |

| GEM30DTAS | CONN EDGECARD 60POS R/A .156 SLD |

| GMM12DRXI | CONN EDGECARD 24POS DIP .156 SLD |

| P1330R-105K | INDUCTOR POWER 1000.0UH SMD |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD9559 | 制造商:AD 制造商全稱(chēng):Analog Devices 功能描述:Dual PLL, Quad Input, Multiservice Line Card Adaptive Clock Translator |

| AD9559/PCBZ | 功能描述:時(shí)鐘和定時(shí)器開(kāi)發(fā)工具 Multi-protocol line card dual clock RoHS:否 制造商:Texas Instruments 產(chǎn)品:Evaluation Modules 類(lèi)型:Clock Conditioners 工具用于評(píng)估:LMK04100B 頻率:122.8 MHz 工作電源電壓:3.3 V |

| AD9559BCPZ | 功能描述:時(shí)鐘發(fā)生器及支持產(chǎn)品 Multi-protocol line card dual clock RoHS:否 制造商:Silicon Labs 類(lèi)型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數(shù)量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-56 |

| AD9559BCPZ-REEL7 | 功能描述:時(shí)鐘發(fā)生器及支持產(chǎn)品 Multi-protocol line card dual clock RoHS:否 制造商:Silicon Labs 類(lèi)型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數(shù)量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-56 |

| AD9559PCBZ | 制造商:AD 制造商全稱(chēng):Analog Devices 功能描述:Dual PLL, Quad Input, Multiservice Line Card Adaptive Clock Translator |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。