- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄16537 > AD9558/PCBZ (Analog Devices Inc)BOARD EVAL FOR AD9558 PDF資料下載

參數(shù)資料

| 型號: | AD9558/PCBZ |

| 廠商: | Analog Devices Inc |

| 文件頁數(shù): | 1/104頁 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL FOR AD9558 |

| 產(chǎn)品變化通告: | AD9558 Minor Metal Mask Change 17/Apr/2012 |

| 設計資源: | AD9558 Eval Brd BOM AD9558 Schematic |

| 標準包裝: | 1 |

| 系列: | * |

當前第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁

Quad Input Multiservice Line Card Adaptive

Clock Translator with Frame Sync

Data Sheet

Rev. B

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibilityisassumedbyAnalogDevicesforitsuse,norforanyinfringementsofpatentsorother

rightsofthirdpartiesthatmayresultfromitsuse.Specificationssubjecttochangewithoutnotice.No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarksandregisteredtrademarksarethepropertyoftheirrespectiveowners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

2011–2013 Analog Devices, Inc. All rights reserved.

FEATURES

Supports GR-1244 Stratum 3 stability in holdover mode

Supports smooth reference switchover with virtually

no disturbance on output phase

Supports Telcordia GR-253 jitter generation, transfer, and

tolerance for SONET/SDH up to OC-192 systems

Supports ITU-T G.8262 synchronous Ethernet slave clocks

Supports ITU-T G.823, G.824, G.825, and G.8261

Auto/manual holdover and reference switchover

4 reference inputs (single-ended or differential)

Input reference frequencies: 2 kHz to 1250 MHz

Reference validation and frequency monitoring (1 ppm)

Programmable input reference switchover priority

20-bit programmable input reference divider

6 pairs of clock output pins with each pair configurable as

a single differential LVDS/HSTL output or as 2 single-ended

CMOS outputs

Output frequencies: 352 Hz to 1250 MHz

Programmable 17-bit integer and 24-bit fractional

feedback divider in digital PLL

Programmable digital loop filter covering loop bandwidths

from 0.1 Hz to 5 kHz (2 kHz maximum for <0.1 dB of

peaking)

Low noise system clock multiplier

Frame sync support

Adaptive clocking

Optional crystal resonator for system clock input

On-chip EEPROM to store multiple power-up profiles

Pin program function for easy frequency translation

configuration

Software controlled power-down

64-lead, 9 mm × 9 mm, LFCSP package

APPLICATIONS

Network synchronization, including synchronous Ethernet

and SDH to OTN mapping/demapping

Cleanup of reference clock jitter

SONET/SDH clocks up to OC-192, including FEC

Stratum 3 holdover, jitter cleanup, and phase transient

control

Wireless base station controllers

Cable infrastructure

Data communications

GENERAL DESCRIPTION

The AD9558 is a low loop bandwidth clock multiplier that

provides jitter cleanup and synchronization for many systems,

including synchronous optical networks (SONET/SDH). The

AD9558 generates an output clock synchronized to up to four

external input references. The digital PLL allows for reduction

of input time jitter or phase noise associated with the external

references. The digitally controlled loop and holdover circuitry

of the AD9558 continuously generates a low jitter output clock

even when all reference inputs have failed.

The AD9558 operates over an industrial temperature range of

40°C to +85°C. If a smaller package is required, refer to the

AD9557 for the two-input/two-output version of the same part.

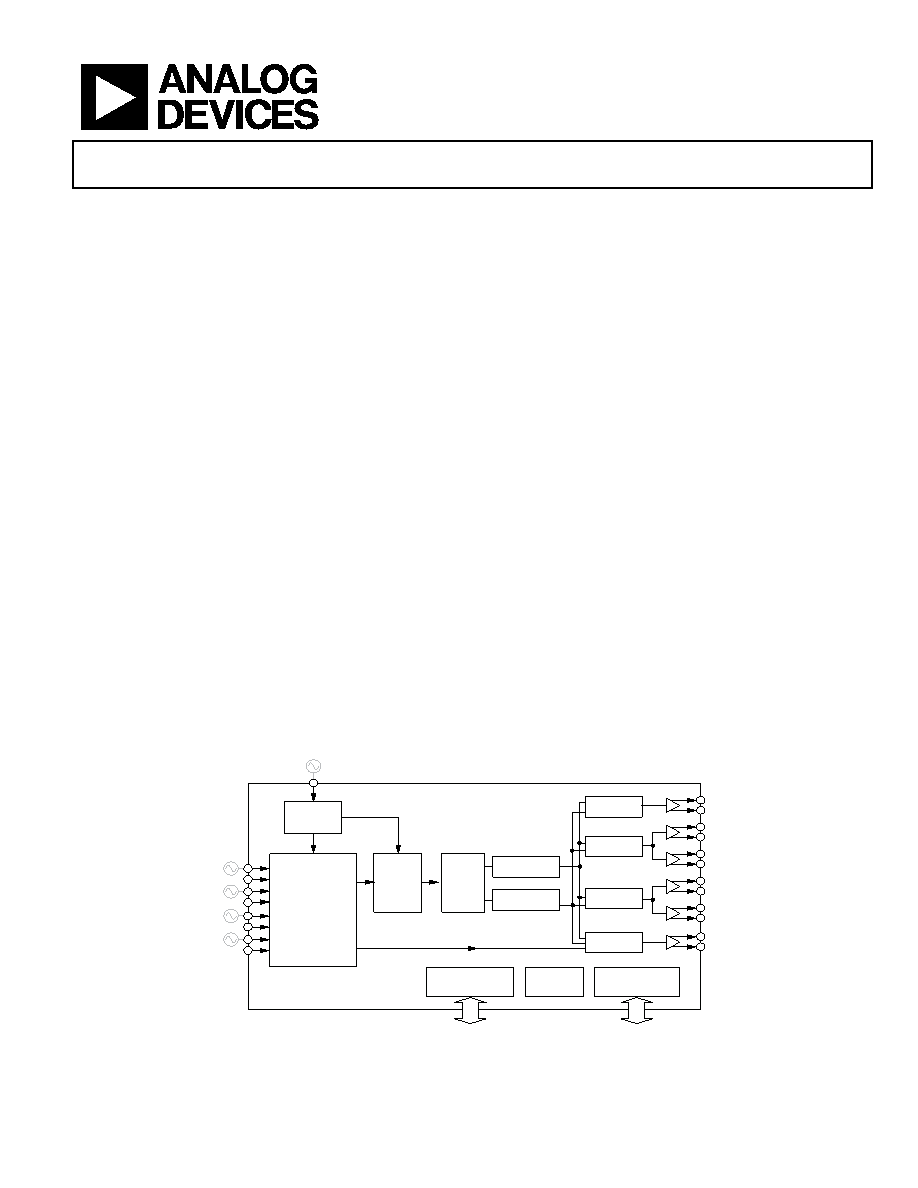

FUNCTIONAL BLOCK DIAGRAM

REFERENCE INPUT

AND

MONITOR MUX

STATUS AND

CONTROL PINS

SERIAL INTERFACE

(SPI OR I2C)

EEPROM

DIGITAL

PLL

CLOCK

MULTIPLIER

STABLE

SOURCE

AD9558

ANALOG

PLL

FRAME SYNC

CHANNEL 1

DIVIDER

CHANNEL 2

DIVIDER

÷3 TO ÷11

HF DIVIDER 0

÷3 TO ÷11

HF DIVIDER 1

CHANNEL 0

DIVIDER

CHANNEL 3

DIVIDER

09758-

001

Figure 1.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| GBM22DSAH | CONN EDGECARD 44POS R/A .156 SLD |

| DK-2632-03 | CABLE FIBER OPTIC DUAL LC-SC 3M |

| GEM30DTAS | CONN EDGECARD 60POS R/A .156 SLD |

| GMM12DRXI | CONN EDGECARD 24POS DIP .156 SLD |

| P1330R-105K | INDUCTOR POWER 1000.0UH SMD |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD9559 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Dual PLL, Quad Input, Multiservice Line Card Adaptive Clock Translator |

| AD9559/PCBZ | 功能描述:時鐘和定時器開發(fā)工具 Multi-protocol line card dual clock RoHS:否 制造商:Texas Instruments 產(chǎn)品:Evaluation Modules 類型:Clock Conditioners 工具用于評估:LMK04100B 頻率:122.8 MHz 工作電源電壓:3.3 V |

| AD9559BCPZ | 功能描述:時鐘發(fā)生器及支持產(chǎn)品 Multi-protocol line card dual clock RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數(shù)量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:QFN-56 |

| AD9559BCPZ-REEL7 | 功能描述:時鐘發(fā)生器及支持產(chǎn)品 Multi-protocol line card dual clock RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數(shù)量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:QFN-56 |

| AD9559PCBZ | 制造商:AD 制造商全稱:Analog Devices 功能描述:Dual PLL, Quad Input, Multiservice Line Card Adaptive Clock Translator |

發(fā)布緊急采購,3分鐘左右您將得到回復。