- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄97869 > DS3131 (MAXIM INTEGRATED PRODUCTS INC) SPECIALTY TELECOM CIRCUIT, PBGA256 PDF資料下載

參數(shù)資料

| 型號: | DS3131 |

| 廠商: | MAXIM INTEGRATED PRODUCTS INC |

| 元件分類: | Telecom IC:Other |

| 英文描述: | SPECIALTY TELECOM CIRCUIT, PBGA256 |

| 封裝: | 27 X 27 MM, PLASTIC, BGA-256 |

| 文件頁數(shù): | 15/174頁 |

| 文件大小: | 1261K |

| 代理商: | DS3131 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁當(dāng)前第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁

DS3131

111 of 174

9.3.4 Done Queue

The DMA writes to the transmit done queue when it has finished either transmitting a complete packet

chain or a complete data buffer. This option is selected by the host when it configures the DQS field in

the transmit DMA configuration RAM (Section 9.3.5). The descriptor location is indicated in the done

queue through a 16-bit pointer that the host uses along with the transmit descriptor base address to find

the exact 32-bit address of the associated transmit descriptor.

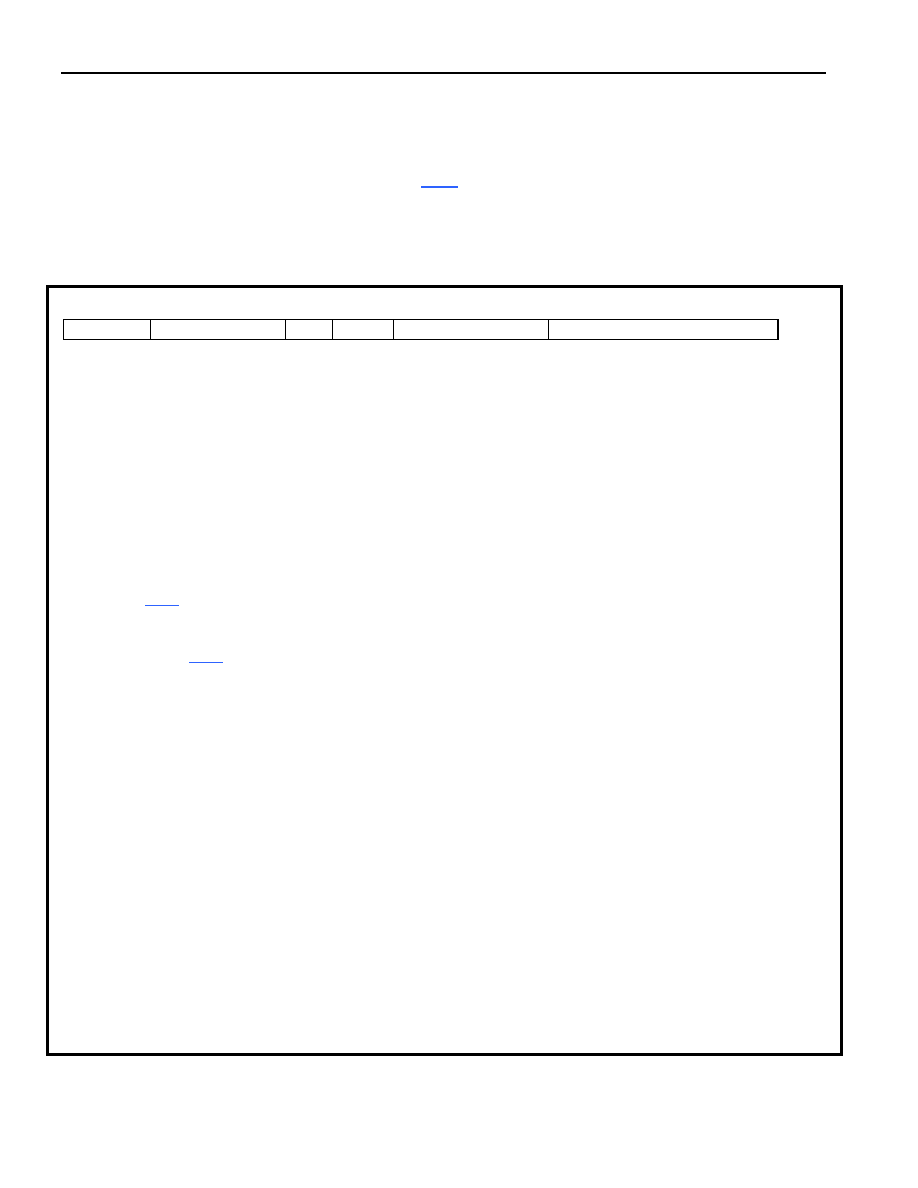

Figure 9-19. Transmit Done-Queue Descriptor

dword 0

Status(3)

CHRST

PRI

00b

HDLC CH#(6)

Descriptor Pointer (16)

Note:

The organization of the done queue is not affected by the enabling of Big Endian.

dword 0; Bits 0 to 15/Descriptor Pointer. This 16-bit value is the offset from the transmit descriptor base

address to either the first descriptor in a HDLC packet (can be a single descriptor) that has been transmitted

(DQS = 0) or the descriptor that corresponds to a single data buffer that has been transmitted (DQS = 1).

dword 0; Bits 16 to 21/HDLC Channel Number. HDLC channel number, which can be from 1 to 40.

000000 (00h) = HDLC channel number 1

100111 (27h) = HDLC channel number 40

dword 0; Bits 22 to 23/Unused. Set to 00b by the DMA.

dword 0; Bit 24/Priority Packet (PRI). This field is meaningless in the done queue and could be set to any value.

See Section 9.3.3 for details.

dword 0; Bit 25/Channel Reset (CH RST). This field is meaningless in the done queue and could be set to any

value. See Section 9.3.3 for details.

dword 0; Bits 26 to 28/Packet Status. These three bits report the final status of an outgoing packet. All of the

error states cause a HDLC abort sequence (eight 1s in a row, followed by continuous interfill bytes of either FFh

or 7Eh) to be sent, and the channel is placed out of service by the transmit DMA, setting the channel enable

(CHEN) bit in the transmit DMA configuration RAM to 0. The status state of 000 is only used when the channel

has been configured by the host to write to the done queue only after a complete HDLC packet (can be a single

data buffer) has been transmitted (i.e., DQS = 0). The status states of 001, 010, and 011 are only used when the

channel has been configured by the host to write to the done queue after each data buffer has been transmitted (i.e.,

DQS = 1).

000 = packet transmission complete and the descriptor pointer field corresponds to the first

descriptor in a HDLC packet (can be a single descriptor) that has been transmitted (DQS = 0)

001 = first buffer transmission complete of a multi- (or single) buffer packet (DQS = 1)

010 = middle buffer transmission complete of a multi-buffer packet (DQS = 1)

011 = last buffer transmission complete of a multi-buffer packet (DQS = 1)

100 = software provisioning error; this channel was not enabled

101 = descriptor error; either byte count = 0 or channel code inconsistent with pending queue

110 = PCI error; abort

111 = transmit FIFO error; it has underflowed

dword 0; Bits 29 to 31/Unused. Not used by the DMA. Could be any value when read.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DS3134 | DATACOM, FRAMER, PBGA256 |

| DS3150QN | DATACOM, PCM TRANSCEIVER, PQCC28 |

| DS3150Q | DATACOM, PCM TRANSCEIVER, PQCC28 |

| DS3150TN | DATACOM, PCM TRANSCEIVER, PDIP48 |

| DS3150T | DATACOM, PCM TRANSCEIVER, PQFP48 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DS3131DK | 功能描述:通信集成電路 - 若干 RoHS:否 制造商:Maxim Integrated 類型:Transport Devices 封裝 / 箱體:TECSBGA-256 數(shù)據(jù)速率:100 Mbps 電源電壓-最大:1.89 V, 3.465 V 電源電壓-最小:1.71 V, 3.135 V 電源電流:50 mA, 225 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝:Tube |

| DS3134 | 功能描述:IC CTRLR HDLC CHATEAU 256-BGA RoHS:否 類別:集成電路 (IC) >> 接口 - 控制器 系列:- 標(biāo)準(zhǔn)包裝:4,900 系列:- 控制器類型:USB 2.0 控制器 接口:串行 電源電壓:3 V ~ 3.6 V 電流 - 電源:135mA 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:36-VFQFN 裸露焊盤 供應(yīng)商設(shè)備封裝:36-QFN(6x6) 包裝:* 其它名稱:Q6396337A |

| DS-313PIN | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog Miscellaneous |

| DS-313-PIN | 功能描述:信號調(diào)節(jié) RoHS:否 制造商:EPCOS 產(chǎn)品:Duplexers 頻率:782 MHz, 751 MHz 頻率范圍: 電壓額定值: 帶寬: 阻抗:50 Ohms 端接類型:SMD/SMT 封裝 / 箱體:2.5 mm x 2 mm 工作溫度范圍:- 30 C to + 85 C 封裝:Reel |

| DS31400 | 制造商:MAXIM 制造商全稱:Maxim Integrated Products 功能描述:8-Input, 14-Output, Dual DPLL Timing IC with Sub-ps Output Jitter |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。