- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369993 > pentium II xeon processor (Intel Corp.) pentium II xeon processor at 400 and 450 MHZ(工作頻率400和450兆赫茲奔II處理器) PDF資料下載

參數(shù)資料

| 型號(hào): | pentium II xeon processor |

| 廠商: | Intel Corp. |

| 英文描述: | pentium II xeon processor at 400 and 450 MHZ(工作頻率400和450兆赫茲奔II處理器) |

| 中文描述: | 奔騰II至強(qiáng)處理器400和450兆赫(工作頻率400和450兆赫茲奔二處理器) |

| 文件頁(yè)數(shù): | 45/97頁(yè) |

| 文件大小: | 978K |

| 代理商: | PENTIUM II XEON PROCESSOR |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)當(dāng)前第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)

E

PENTIUM II XEON PROCESSOR AT 400 AND 450 MHZ

45

12/15/98 5:14 PM 24377002.doc

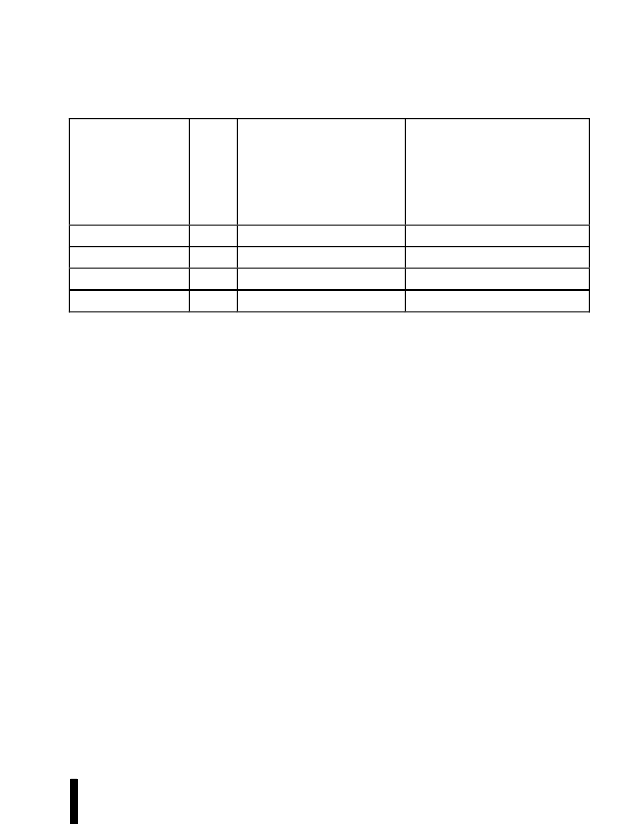

Table 23. Processor Information ROM Format

(Continued)

32

Cartridge Feature Flags

[6] = Serial Signature

[5] = Electronic Signature Present

[4] = Thermal Sense Device Present

[3] = Thermal Reference Byte

Present

[2] = OEM EEPROM Present

[1] = Core VID Present

[0] = L2 Cache VID Present

4

Number of Devices in TAP Chain

One 4-bit hex digit

4

Reserved

Reserved for future use

8

Checksum

1 byte checksum

OTHER: 7Eh

16

Reserved

Reserved for future use

4.3.2.

SCRATCH EEPROM

Also available on the SMBus is an EEPROM which

may be used for other data at the system or

processor vendor’s discretion. The data in this

EEPROM, once programmed, can be write-protected

by asserting the active-high WP signal. This signal

has a weak pull-down (10k

) to allow the EEPROM

to be programmed in systems with no implementation

of this signal. The Scratch EEPROM is a 1024 bit

part.

4.3.3.

PROCESSOR INFORMATION ROM

AND SCRATCH EEPROM

SUPPORTED SMBUS TRANSACTIONS

The Processor Information ROM responds to three

SMBus packet types: current address read, random

address read, and sequential read. The Scratch

EEPROM responds to two additional packet types:

byte write and page write. Table 24 diagrams the

current address read. The internal address counter

keeps track of the address accessed during the last

read or write operation, incremented by one. Address

“roll over” during reads is from the last byte of the last

eight byte page to the first byte of the first page. “Roll

over” during writes is from the last byte of the current

eight byte page to the first byte of the same page.

Table 25 diagrams the random read. The write with

no data loads the address desired to be read.

Sequential reads may begin with a current address

read or a random address read. After the SMBus

host controller receives the data word it responds

with an acknowledge. This will continue until the

SMBus host controller responds with a negative

acknowledge and a stop. Table 26 diagrams the byte

write. The page write operates the same way as the

byte write except that the SMBus host controller

does not send a stop after the first data byte and

acknowledge. The Scratch EEPROM internally

increments its address. The SMBus host controller

continues to transmit data bytes until it terminates the

sequence with a stop. All data bytes will result in an

acknowledge from the Scratch EEPROM. If more

than eight bytes are written the internal address will

“roll over” and the previous data will be overwritten.

In the tables, ‘S’ represents the SMBus start bit, ‘P’

represents a stop bit, ‘R’ represents a read bit, ‘W’

represents

a

write

bit,

acknowledge, and ‘///’ represents a negative

acknowledge. The shaded bits are transmitted by the

Processor Information ROM or Scratch EEPROM

and the bits that aren’t shaded are transmitted by the

SMBus host controller. In the tables the data

addresses indicate 8 bits. The SMBus host controller

should transmit 8 bits, but as there are only 128

addresses, the most significant bit is a don’t care.

‘A’

represents

an

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| Pentium III cpu with mobile | Pentium III processor Mobile Module Connector 2 (MMC-2)(帶移動(dòng)模塊連接器2奔III處理器) |

| pentium III CPU | Pentium III Processor for the SC242 at 450MHz to 1.0GHz(SC242工作頻率450MHZ到1GHZ奔III處理器) |

| pentium III processor | 32 bit Processor Mobile Module(32 位帶移動(dòng)模塊處理器) |

| Pentium OverDrive Processor | Pentium OverDrive Processor With MMX Technology For Pentium Processor-Based System(帶MMX技術(shù)奔騰超速轉(zhuǎn)動(dòng)處理器) |

| pentium pro processor | Pentium Pro Processor with 1MB L2 Cache at 200MHZ(1兆比特L2高速緩存頻率200兆赫茲處理器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| P-ENV568K3G3 | 制造商:Panasonic Industrial Company 功能描述:TUNER |

| PEO14012 | 制造商:TE Connectivity 功能描述:RELAY SPCO 12VDC |

| PEO14024 | 制造商:TE Connectivity 功能描述:RELAY SPCO 24VDC |

| PEO96742 | 制造商:Delphi Corporation 功能描述:ASM TERM |

| PEOODO3A | 制造商:MACOM 制造商全稱:Tyco Electronics 功能描述:Versatile Power Entry Module with Small Footprint |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。