- 您現在的位置:買賣IC網 > PDF目錄98007 > M44C510D-XXX-DOW (TEMIC SEMICONDUCTORS) 4-BIT, MROM, MICROCONTROLLER PDF資料下載

參數資料

| 型號: | M44C510D-XXX-DOW |

| 廠商: | TEMIC SEMICONDUCTORS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 4-BIT, MROM, MICROCONTROLLER |

| 封裝: | SSOP-44 |

| 文件頁數: | 16/60頁 |

| 文件大小: | 709K |

| 代理商: | M44C510D-XXX-DOW |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁當前第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁

M44C510E

Preliminary Information

Rev. A1, 04-May-00

23 (60)

the interrupt edge and programming of the interrupt

priority levels. When programming or reprogramming ei-

ther of the port monitor control registers, any previously

generated interrupt on that port which has not yet been ac-

knowledged by the CPU or an interrupt generated by the

reprogramming itself is automatically cleared. Port A can

also be used for a mask programmable coded reset. For

more information see section 1.4 ’Hardware Reset’.

The Port Interrupt Priority Registers PAIPR and PBIPR

are I/O mapped to the the primary address registers of the

Port Monitor Module addresses ’2’h and ’3’h respec-

tively. The Port Interrupt Control Registers PAICR and

PBICR are mapped to the corresponding auxiliary

registers.

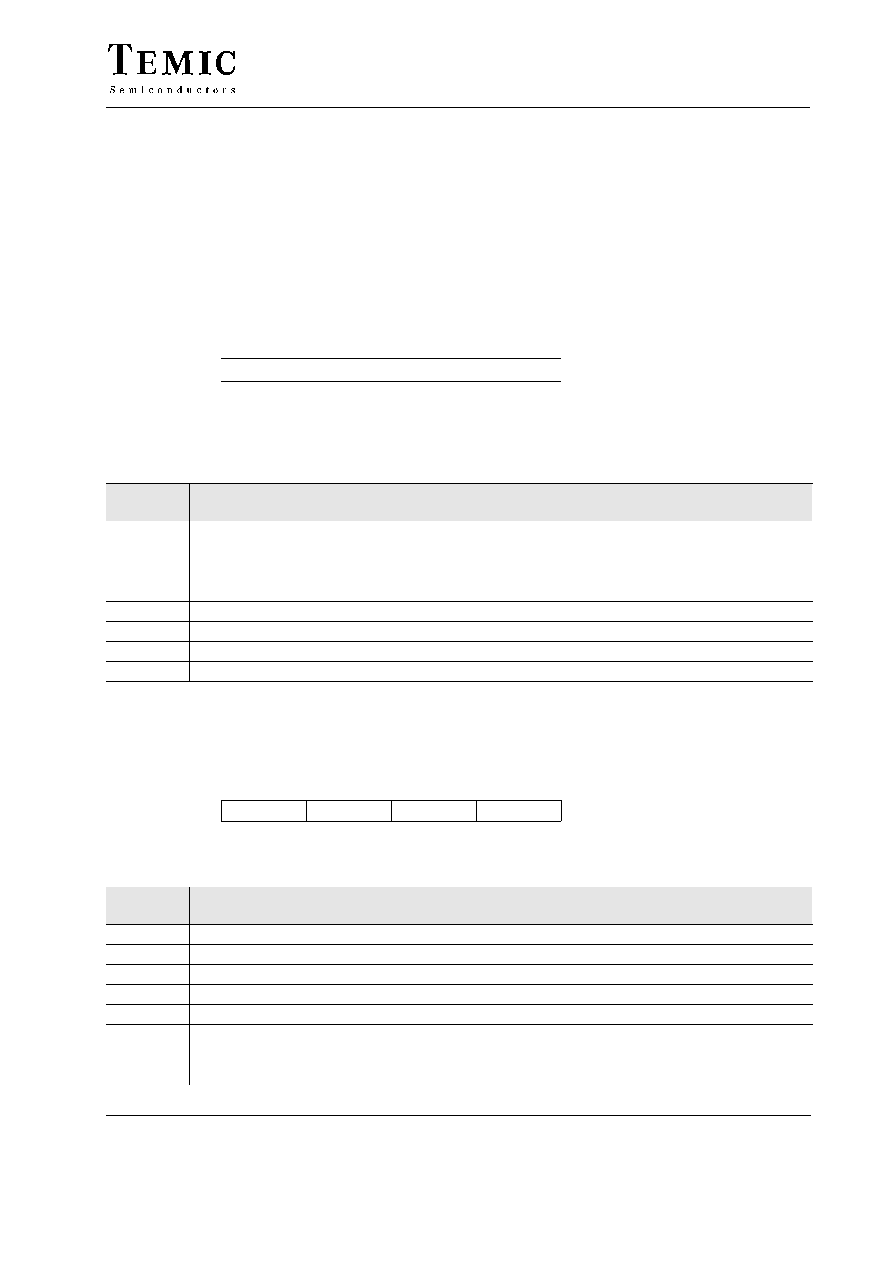

Port Monitor Interrupt Priority Register (PxIPR)

x = ’A’ (Port A) or ’B’ (Port B)

(Port A) Primary register address: ’2’hex

(Port B) Primary register address: ’3’hex

Bit 3

Bit 2

Bit 1

Bit 0

PxIPR

IMx

ITRx

PRx2

PRx1

Reset value: 1111b

IMx

– Interrupt Mask

ITRx

– Interrupt Transition

PRx2..1

– Interrupt Priority code

Table 10. Port Monitor Interrupt Priority Register (PxIPR)

Code

3 2 1 0

Function

x x 0 0

Port monitor interrupt priority 7

x x 0 1

Port monitor interrupt priority 5

x x 1 0

Port monitor interrupt priority 3

x x 1 1

Port monitor interrupt priority 1

x 0 x x

Port monitor interrupt on falling edge

x 1 x x

Port monitor interrupt on rising edge

0 x x x

Port monitor interrupt enabled

1 x x x

Port monitor interrupt disabled

Port Monitor Interrupt Control Register (PxICR)

x = ’A’ (Port A) or ’B’ (Port B)

(Port A) Auxiliary register address: ’2’hex

(Port B) Auxiliary register address: ’3’hex

Bit 3

Bit 2

Bit 1

Bit 0

PxICR

ENx3

ENx2

ENx1

ENx0

Reset value: 1111b

ENx3 ... 0 port monitor input ENable code

Table 11. Port Monitor Interrupt Control Register (PxICR)

Code

3 2 1 0

Function

x x x 0

Bit 0 can generate an interrupt

x x x 1

Bit 0 cannot generate an interrupt

x x 0 x

Bit 1 can generate an interrupt

x x 1 x

Bit 1 cannot generate an interrupt

x 0 x x

Bit 2 can generate an interrupt

x 1 x x

Bit 2 cannot generate an interrupt

0 x x x

Bit 3 can generate an interrupt

1 x x x

Bit 3 cannot generate an interrupt

相關PDF資料 |

PDF描述 |

|---|---|

| M44C588 | 4-BIT, MROM, 4 MHz, MICROCONTROLLER |

| M44C892 | 4-BIT, MROM, 4 MHz, MICROCONTROLLER, PDSO20 |

| M48T08Y-15PC1 | 0 TIMER(S), REAL TIME CLOCK, PDMA28 |

| M48T08Y-10PC1 | 0 TIMER(S), REAL TIME CLOCK, PDMA28 |

| M48T128Y-70PM1 | 0 TIMER(S), REAL TIME CLOCK, PDIP32 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| M44C890 | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:Low-Current Microcontroller for Wireless Communication |

| M44C890-H | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:Low-Current Microcontroller for Wireless Communication |

| M44S05K4F1 | 功能描述:汽車連接器 MX44 Terminals RoHS:否 制造商:Amphenol SINE Systems 產品:Contacts 系列:ATP 位置數量: 型式:Female 安裝風格: 端接類型: 觸點電鍍:Nickel |

| M44T332538880MHZ | 制造商:MEC 功能描述: |

| M44T3338880MHZ | 制造商:MEC 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復。