- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370261 > FW82439TX Controller Miscellaneous - Datasheet Reference PDF資料下載

參數(shù)資料

| 型號(hào): | FW82439TX |

| 英文描述: | Controller Miscellaneous - Datasheet Reference |

| 中文描述: | 控制器雜項(xiàng)-數(shù)據(jù)表參考 |

| 文件頁(yè)數(shù): | 55/102頁(yè) |

| 文件大?。?/td> | 759K |

| 代理商: | FW82439TX |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)當(dāng)前第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)

Extended Temperature 82439TX (MTXC) Datasheet

55

PRELIMINARY

Rules for Populating SIMM Modules (or x32 SO-DIMM modules)

SIMM sockets can be populated in any order (i.e., memory for RAS0# does not have to be populated

before memory for RAS[2:1]# or RAS[4:3]# are used).

SIMM socket pairs (i.e., two, 32-bit wide SIMMs) need to be populated with the same densities. For

example, SIMM sockets for RAS0# should be populated with identical densities. However, SIMM sockets

for RAS[2:1]# can be populated with different densities than the SIMM socket pair for RAS0#.

EDOs and standard page mode can both be used; however, only one type should be used per SIMM

socket pair. For example, in the table shown below SIMM sockets for RAS[2:1]# can be populated with

EDOs while SIMM sockets for RAS[4:3]# can be populated with standard page mode. If different memory

is used for different rows, each row will be optimized for that type of memory.

The DRAM Timing Register which provides the DRAM speed grade control for the entire memory array

must be programmed to use the timings of the slowest DRAMs installed.

Rules for Populating DIMM or SO-DIMM modules

DIMM or SO-DIMM sockets can be populated in any order (i.e., memory for RAS0# does not have to be

populated before memory for RAS[2:1]# or RAS[4:3]# are used).

4.3.2.

CONFIGURATION REQUIREMENTS

General Configuration Requirements

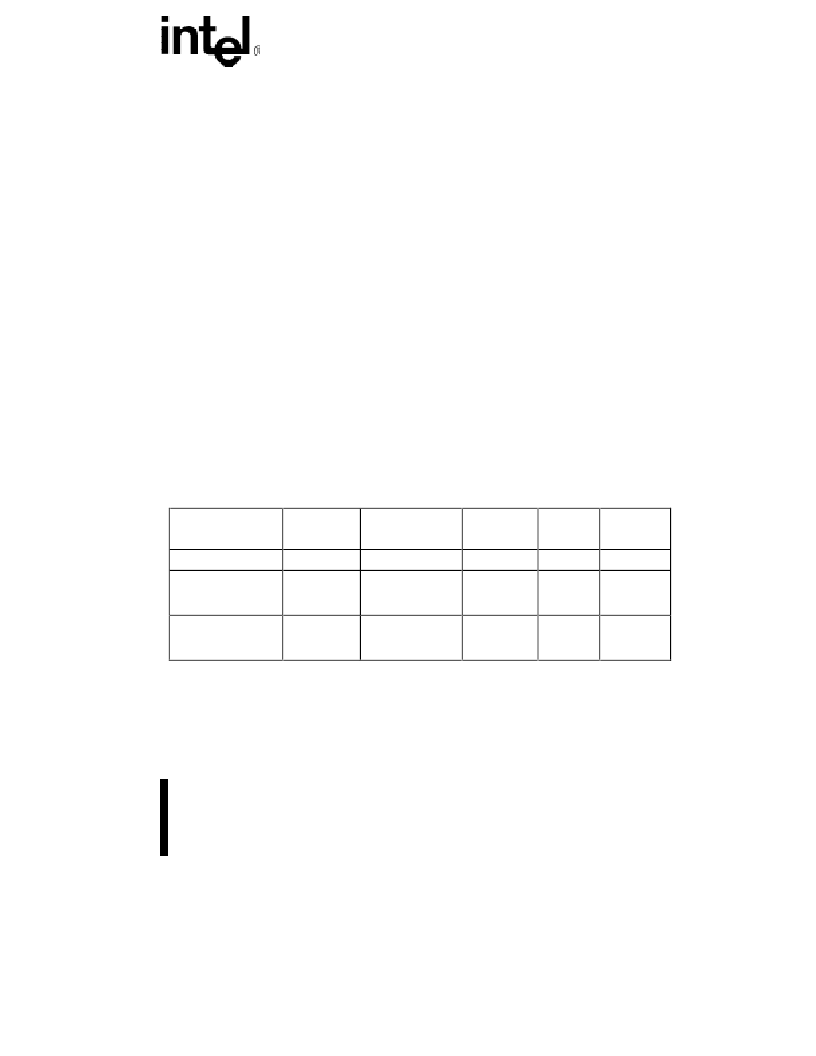

In a system that uses 64-Mbit SDRAM, the RAS4#/CS4#/BA1 and RAS5#/CS5#/MA13 signals are used

to provide two additional address lines (BA1 and MA13), and KRQAK/CS4_64# is used to provide the 5th

CS# line, if required. To enable 64-Mbit support for four rows of SDRAM, set SDRAMC[bit 1] to 1 (offset

54h). To enable 64-Mbit support for five rows of SDRAM, SDRAMC[bit 1] must be set to 1, and DRAM

cache must

not

be present in the system (indicated by CEC[bit 5]=0, offset 53h). In a five row SDRAM

system that supports 64-Mbit SDRAM devices, the KRQAK/CS4_64# signal provides the fifth CS# (or

CS4_64#) function. This means that a system that supports DRAM Cache, can not support five rows of

64-Mbit SDRAM. However, four rows of 64-Mbit SDRAM with DRAM Cache is supported. In a FPM/EDO

only configuration, there are no restrictions on using 64-Mbit devices (i.e., all six rows can support 64-

Mbit DRAM devices. However, SDRAMC[bit 1] must be set to 1 if more than four rows of EDO/FPM are

used. This allows the RAS4# and RAS5# functions to be used.

Driven on

RAS5#/CS5#/

MA13

Driven on

RAS4#/CS4#/

MA13

Driven on

KRQAK/

CS4_64#

64-Mbit

(SDRAM)

64-Mbit

(EDO/FPM)

Bit 1, reg 54h=0

RAS5#/CS5#

RAS4#/CS4#

KRQAK

no

yes (6 rows)

Bit 1, reg 54h=1 and

DRAM Cache is

present*

MA13

BA1 (Bank Select)

KRQAK

Yes

(4 rows)

Yes (4 rows)

Bit 1, reg 54h=1 and

DRAM Cache is not

present

1

MA13

BA1 (Bank Select)

RAS4#/

CS4_64#

Yes

(5 rows)

Yes (5 rows)

NOTES:

1.

The presence of DRAM cache is indicated by the value in bit 5, register 53h.

Due to loading, using SDRAM x4 devices is not recommended.

Buffering of SDRAM Rows is not supported

In a five row system, the 5th row is intended to be implemented with DRAM devices that are soldered

down on the motherboard. If a DIMM or a SIMM is used in the 5th row, it should

not

be used as an

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| FW82815 | Controller Miscellaneous - Datasheet Reference |

| FWA-25A10F | Fuse |

| FWA-30A10F | Fuse |

| FWA-35A21F | Fuse |

| FWA-40A21F | Fuse |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| FW82439TX S L28T | 制造商:Intel 功能描述:System Controller 324-Pin BGA |

| FW82439TX S L3BT | 制造商:Intel 功能描述:System Controller |

| FW82439TX S L28T | 制造商:Intel 功能描述: |

| FW82439TX S L3BT | 制造商:Intel 功能描述:System Controller |

| FW82439TXSL28T | 功能描述:IC 82439TX SYS CTRL MTXC 324BGA RoHS:否 類別:集成電路 (IC) >> 接口 - 控制器 系列:- 標(biāo)準(zhǔn)包裝:4,900 系列:- 控制器類型:USB 2.0 控制器 接口:串行 電源電壓:3 V ~ 3.6 V 電流 - 電源:135mA 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:36-VFQFN 裸露焊盤(pán) 供應(yīng)商設(shè)備封裝:36-QFN(6x6) 包裝:* 其它名稱:Q6396337A |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。