- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371435 > 28F3204C3 (Intel Corp.) 3 V Advanced+ Stacked Chip Scale Package Memory(3V高級(jí)堆芯片封裝存儲(chǔ)器) PDF資料下載

參數(shù)資料

| 型號(hào): | 28F3204C3 |

| 廠商: | Intel Corp. |

| 英文描述: | 3 V Advanced+ Stacked Chip Scale Package Memory(3V高級(jí)堆芯片封裝存儲(chǔ)器) |

| 中文描述: | 3伏高級(jí)堆疊芯片級(jí)封裝存儲(chǔ)器(3V的高級(jí)堆芯片封裝存儲(chǔ)器) |

| 文件頁數(shù): | 8/62頁 |

| 文件大?。?/td> | 538K |

| 代理商: | 28F3204C3 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁當(dāng)前第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁

28F1602C3, 28F3204C3

E

8

PRODUCT PREVIEW

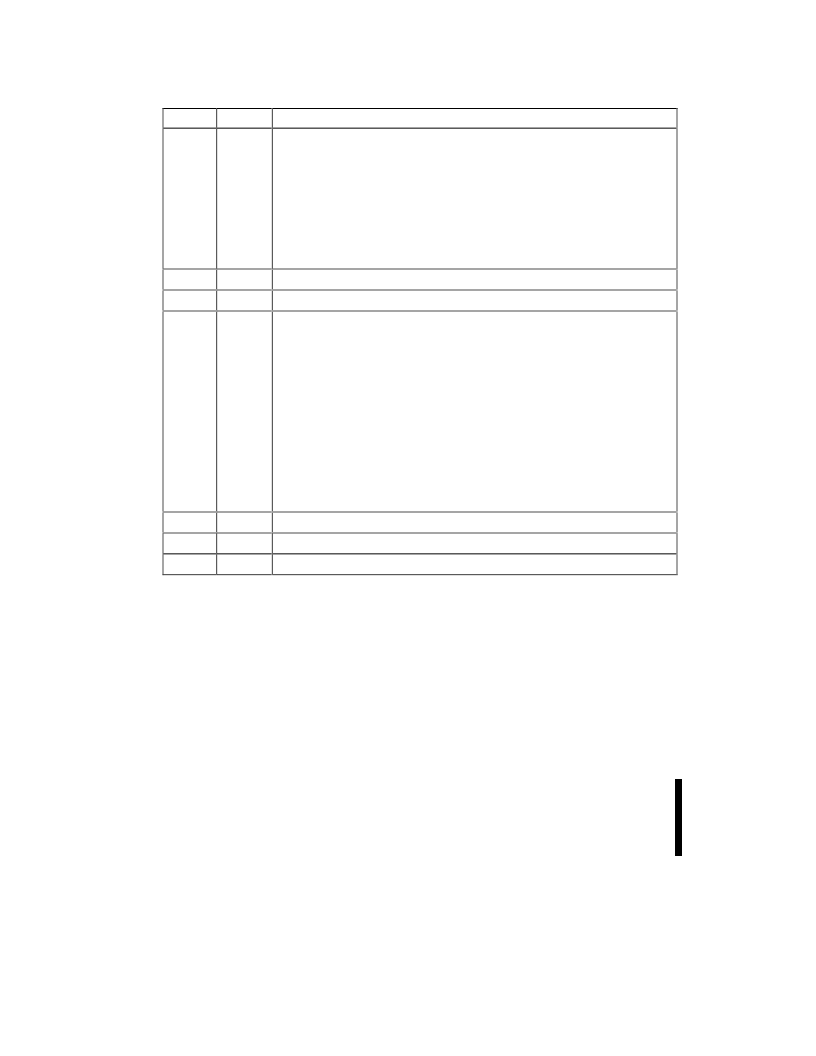

Table 1. 3 Volt Advanced+ Stacked-CSP Ball Descriptions

(Continued)

Symbol

Type

Name and Function

F-WP#

INPUT

FLASH WRITE PROTECT:

Controls the lock-down function of the flexible

Locking feature.

When F-WP# is a logic low, the lock-down mechanism is enabled

and blocks

marked lock-down cannot be unlocked through software.

When F-WP# is logic high, the lock-down mechanism is disabled

and blocks

previously locked-down are now locked and can be unlocked and locked through

software. After F-WP# goes low, any blocks previously marked lock-down revert

to that state.

See Section 6.0 for details on block locking.

F-V

CC

SUPPLY

FLASH POWER SUPPLY:

[2.7 V

–3.3 V] Supplies power for device operations.

S-V

CC

SUPPLY

SRAM POWER SUPPLY:

[2.7 V–3.3 V] Supplies power for device operations.

F-V

PP

INPUT /

SUPPLY

FLASH PROGRAM/ERASE POWER SUPPLY:

[1.65 V–3.3 V or 11.4 V–12.6 V]

Operates as a input at logic levels to control complete flash protection. Supplies

power for accelerated flash program and erase operations in 12 V

±

5% range.

This ball cannot be left floating.

Lower

F-

V

PP

≤

V

PPLK

, to protect all contents

against Program and Erase

commands.

Set

F-

V

PP

=

F-

V

CC

for in-system read, program and erase operations

. In this

configuration, F-V

PP

can drop as low as 1.65 V to allow for resistor or diode drop

from the system supply. Note that if F-V

PP

is driven by a logic signal, V

IH =

1.65 V.

That is, F-V

PP

must remain above 1.65 V to perform in-system flash modifications.

Raise

F-

V

PP

to 12 V

±

5% for faster program and erase

in a production

environment. Applying 12 V

±

5% to F-V

PP

can only be done for a maximum of

1000 cycles on the main blocks and 2500 cycles on the parameter blocks.

F-V

PP

may be connected to 12 V for a total of 80 hours maximum.

F-GND

SUPPLY

FLASH GROUND:

For all internal circuitry. All ground inputs

must

be connected.

S-GND

SUPPLY

SRAM GROUND:

For all internal circuitry. All ground inputs

must

be connected.

DU

DON’T USE: Do not drive ball to V

IH

or V

IL

. Leave unconnected.

3.0

STACKED CHIP SCALE

PACKAGE ORGANIZATION

The 3 Volt Advanced+ Stacked-CSP contains a

flash and a SRAM component. The flash device is

asymmetrically-blocked

integration of code and data storage in a single

device.

Each

flash

block

independently of the others up to 100,000 times.

For the address locations of each flash block, see

the memory maps in Appendix C.

to

enable

system

can

be

erased

Figure 2 illustrates the Stacked-CSP block diagram.

4.0

PRINCIPLES OF OPERATION

The 3 Volt Advanced+ Stacked-CSP incorporates

flash and SRAM in a single package.

The flash memory utilizes a CUI and automated

algorithms

to

simplify

operations. The internal algorithms are controlled

by an internal WSM. The CUI handles the interface

to the data and address latches, as well as system

status requests during WSM operation.

program

and

erase

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 28F1604C3 | 3 Volt Advanced+ Stacked Chip Scale Package Memory(3V閃速存儲(chǔ)器和靜態(tài)存儲(chǔ)器) |

| 28F160C18 | 1.8V Advanced+ Boot Block Flash Memory(1.8V高級(jí)引導(dǎo)塊閃速存儲(chǔ)器) |

| 28F160C2 | 2.4V Advanced+ Boot Block Flash Memory(2.4V高級(jí)引導(dǎo)塊閃速存儲(chǔ)器) |

| 28F800C2 | 2.4V Advanced+ Boot Block Flash Memory(2.4V高級(jí)引導(dǎo)塊閃速存儲(chǔ)器) |

| 28F160S3 | 3 V FlashFile Memory(3 V FlashFile 存儲(chǔ)器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 28F3204W30 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:1.8 Volt Intel Wireless Flash Memory with 3 Volt I/O and SRAM (W30) |

| 28F320B3 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:SMART 3 ADVANCED BOOT BLOCK 4-, 8-, 16-, 32-MBIT FLASH MEMORY FAMILY |

| 28F320C3 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Advanced+ Boot Block Flash Memory (C3) |

| 28F320J3D75 | 制造商:undefined 功能描述: |

| 28F320J5 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:StrataFlash MEMORY TECHNOLOGY 32 AND 64 MBIT |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。