- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371435 > 28F3204C3 (Intel Corp.) 3 V Advanced+ Stacked Chip Scale Package Memory(3V高級(jí)堆芯片封裝存儲(chǔ)器) PDF資料下載

參數(shù)資料

| 型號(hào): | 28F3204C3 |

| 廠商: | Intel Corp. |

| 英文描述: | 3 V Advanced+ Stacked Chip Scale Package Memory(3V高級(jí)堆芯片封裝存儲(chǔ)器) |

| 中文描述: | 3伏高級(jí)堆疊芯片級(jí)封裝存儲(chǔ)器(3V的高級(jí)堆芯片封裝存儲(chǔ)器) |

| 文件頁(yè)數(shù): | 19/62頁(yè) |

| 文件大?。?/td> | 538K |

| 代理商: | 28F3204C3 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)當(dāng)前第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)

E

7.3

28F1602C3, 28F3204C3

19

PRODUCT PREVIEW

Locking the Protection Register

The user-programmable segment of the protection

register is lockable by programming Bit 1 of the

PR-LOCK location to 0. Bit 0 of this location is

programmed to 0 at the Intel factory to protect the

unique device number. This bit is set using the

Protection Program command to program

“FFFD” to

the PR-LOCK location. After these bits have been

programmed, no further changes can be made to

the values stored in the protection register.

Protection Program commands to a locked section

will result in a status register error (program error bit

SR.4 and Lock Error bit SR.1 will be set to 1).

Protection register lockout state is not reversible.

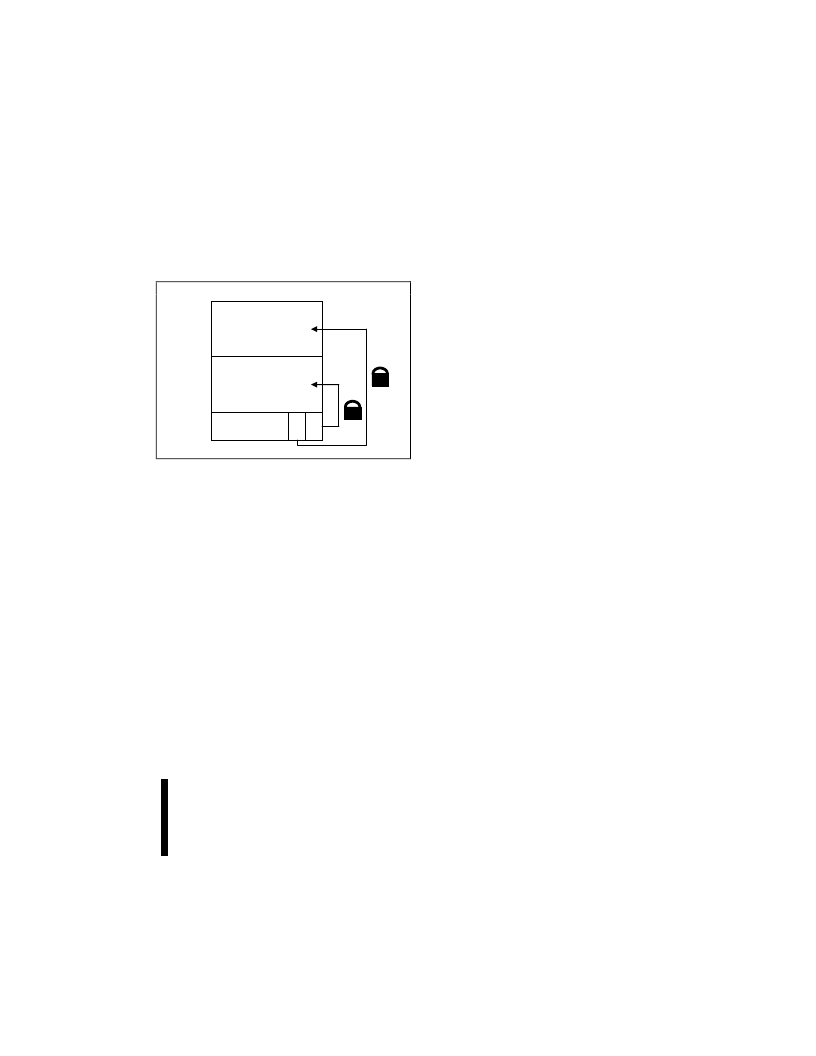

4 Words

Factory Programmed

4 Words

User Programmed

PR-LOCK

88H

85H

84H

81H

80H

0645_05

Figure 3. Protection Register Memory Map

8.0

FLASH MEMORY PROGRAM

AND ERASE VOLTAGES

Intel 3 Volt Advanced+ Stacked-CSP products

provide in-system programming and erase in the

1.65 V–3.3 V

range.

programming, it also includes a low-cost, backward-

compatible 12 V programming feature.

For

fast

production

8.1

Improved 12 Volt Production

Programming

When F-V

PP

is between 1.65 V and 3.3 V, all

program and erase current is drawn through the

F-V

CC

signal. Note that if F-V

PP

is driven by a logic

signal, V

IH

min = 1.65 V. That is, F-V

PP

must remain

above

1.65 V

to

perform

modifications. When F-V

PP

is connected to a 12 V

power supply, the device draws program and erase

current directly from the F-V

PP

signal. This

eliminates the need for an external switching

transistor to control the voltage F-V

PP

. Figure 12

shows examples of how the flash power supplies

can be configured for various usage models.

in-system

flash

The 12 V F-V

PP

mode enhances programming

performance during the short period of time typically

found in manufacturing processes; however, it is

not intended for extended use. 12 V may be applied

to F-V

PP

during program and erase operations for a

maximum of 1000 cycles on the main blocks and

2500 cycles on the parameter blocks. F-V

PP

may

be connected to 12 V for a total of 80 hours

maximum. Stressing the device beyond these limits

may cause permanent damage.

8.2

F-V

≤

V

for Complete

Protection

In addition to the flexible block locking, the F-V

PP

programming voltage can be held low for absolute

hardware write protection of all blocks in the flash

device. When F-V

PP

is below V

PPLK

, any program or

erase operation will result in a error, prompting the

corresponding status register bit (SR.3) to be set.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 28F1604C3 | 3 Volt Advanced+ Stacked Chip Scale Package Memory(3V閃速存儲(chǔ)器和靜態(tài)存儲(chǔ)器) |

| 28F160C18 | 1.8V Advanced+ Boot Block Flash Memory(1.8V高級(jí)引導(dǎo)塊閃速存儲(chǔ)器) |

| 28F160C2 | 2.4V Advanced+ Boot Block Flash Memory(2.4V高級(jí)引導(dǎo)塊閃速存儲(chǔ)器) |

| 28F800C2 | 2.4V Advanced+ Boot Block Flash Memory(2.4V高級(jí)引導(dǎo)塊閃速存儲(chǔ)器) |

| 28F160S3 | 3 V FlashFile Memory(3 V FlashFile 存儲(chǔ)器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 28F3204W30 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:1.8 Volt Intel Wireless Flash Memory with 3 Volt I/O and SRAM (W30) |

| 28F320B3 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:SMART 3 ADVANCED BOOT BLOCK 4-, 8-, 16-, 32-MBIT FLASH MEMORY FAMILY |

| 28F320C3 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Advanced+ Boot Block Flash Memory (C3) |

| 28F320J3D75 | 制造商:undefined 功能描述: |

| 28F320J5 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:StrataFlash MEMORY TECHNOLOGY 32 AND 64 MBIT |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。