- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98007 > M44C588 (TEMIC SEMICONDUCTORS) 4-BIT, MROM, 4 MHz, MICROCONTROLLER PDF資料下載

參數(shù)資料

| 型號: | M44C588 |

| 廠商: | TEMIC SEMICONDUCTORS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 4-BIT, MROM, 4 MHz, MICROCONTROLLER |

| 文件頁數(shù): | 3/44頁 |

| 文件大小: | 549K |

| 代理商: | M44C588 |

第1頁第2頁當(dāng)前第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁

M44C588

Preliminary Information

TELEFUNKEN Semiconductors

Rev. A1, 11-Nov-97

11 (44)

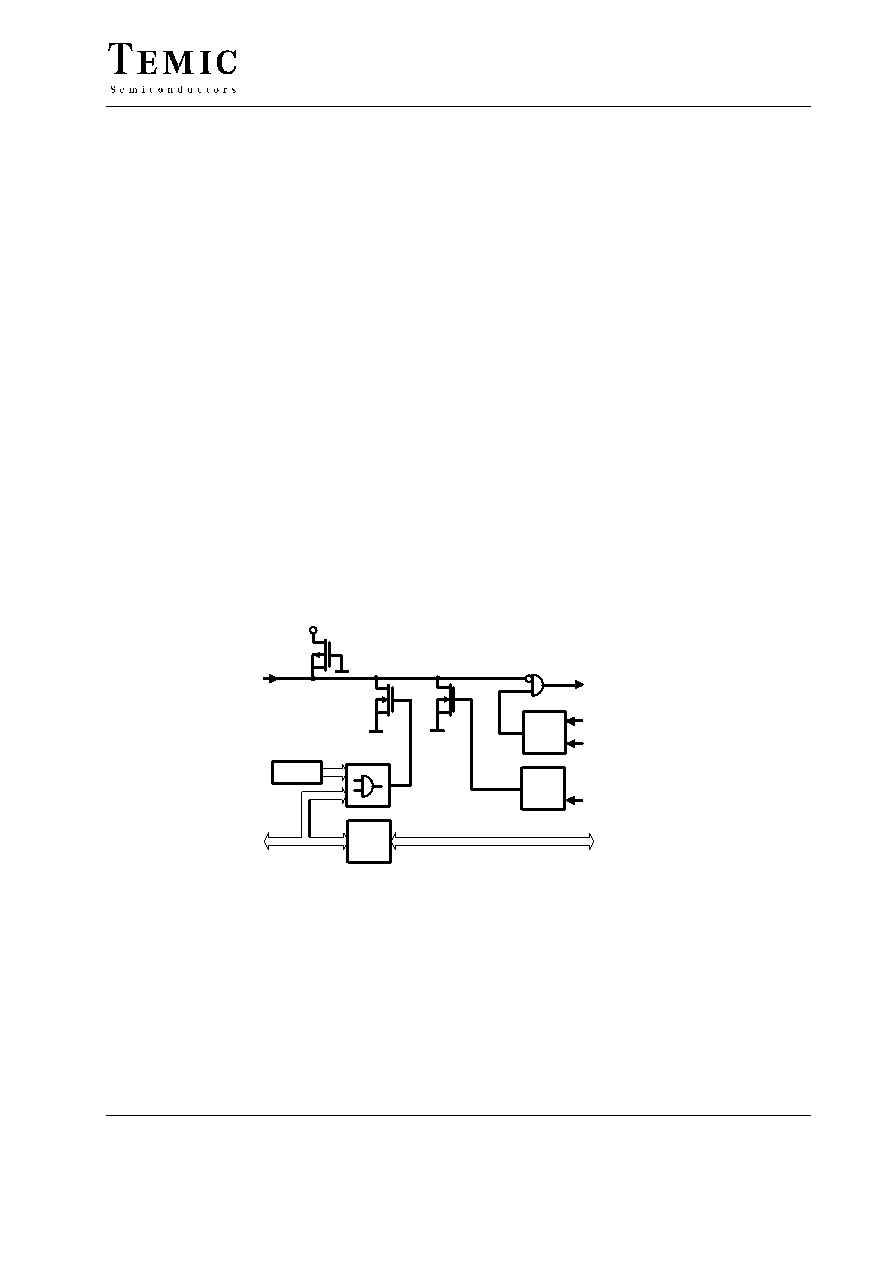

the current program state. It can be triggered by either ini-

tial supply power-up, a short collapse of the power supply,

a watchdog time out, activation of the NRST input or the

occurrence of a coded reset on Port B (see figure 9).

A master reset activation will reset the interrupt enable

flag, the interrupt pending register and the interrupt active

register. During the reset phase the I/O bus control signals

are set to ’reset mode’ thereby initializing all on-chip

peripherals.

Releasing the reset results in a short call instruction (op-

code C1h) to the ROM address 008h. This activates the

initialization routine $RESET which in turn initialises all

necessary RAM variables, stack pointers and peripheral

configuration registers.

Power-on Reset

The fully integrated power-on reset circuit ensures that

the core is held in a reset state until the minimum operat-

ing supply voltage has been reached. A reset condition

will also be generated should the supply voltage drop

momentarily below the minimum operating supply.

External Reset (NRST)

An external reset can be triggered with the NRST pin. To

activate an external reset the pin should be low for a

minimum of two machine cycles.

Coded Reset (Port B)

The coded reset circuit is connected directly to the Port B

terminals. Using a mask option, the user can define a

hardwired code combination (e.g. all pins low) which, if

occurring on the Port B will generate a reset in the same

way as the NRST pin.

Note that if this option is used, the reset is not maskable

and will also trigger if the predefined code is written on

to the Port B by the CPU itself. Care should also be taken

not to generate an unwanted reset by inadvertently pass-

ing through the reset code on input transitions. This

applies especially if the pins have a high capacitive load-

ing.

Watchdog Reset

The watchdog can be activated by using a mask option

and triggers a reset with every watchdog counter over-

flow. To suppress the watchdog reset, the counter must be

regularly reset by reading the watchdog register address

(WDRES).

The CPU reacts in exactly the same manner as a reset

stimulus from any of the above sources

Port B

I/O

reset code

CPU

NRST

V

Watch-

Power-on

reset

CPU reset

rst

Pull-up

CODE *

time out

V

WD reset

* = Mask option

dog *

DD

SS

DD

96 115

Figure 9. Reset configuration

1.5

Clock Generation

1.5.1

Clock Module

The M44C588 contains a clock module with 4 different

internal oscillator types: two RC-oscillators, one 4-MHz

crystal oscillator and one 32-kHz crystal oscillator. The

pins OSCIN and OSCOUT are the interface to connect a

crystal either to the 4-MHz, or to the 32-kHz crystal

oscillator. SCLIN can be used as input for external clocks

or to connect an external trimming resistor for the

RC-oscillator 2. All necessary circuitry except the crystal

and the trimming resistor is integrated on-chip. One of

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M44C892 | 4-BIT, MROM, 4 MHz, MICROCONTROLLER, PDSO20 |

| M48T08Y-15PC1 | 0 TIMER(S), REAL TIME CLOCK, PDMA28 |

| M48T08Y-10PC1 | 0 TIMER(S), REAL TIME CLOCK, PDMA28 |

| M48T128Y-70PM1 | 0 TIMER(S), REAL TIME CLOCK, PDIP32 |

| M48T128Y-85PM1 | 0 TIMER(S), REAL TIME CLOCK, PDIP32 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M44C890 | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:Low-Current Microcontroller for Wireless Communication |

| M44C890-H | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:Low-Current Microcontroller for Wireless Communication |

| M44S05K4F1 | 功能描述:汽車連接器 MX44 Terminals RoHS:否 制造商:Amphenol SINE Systems 產(chǎn)品:Contacts 系列:ATP 位置數(shù)量: 型式:Female 安裝風(fēng)格: 端接類型: 觸點電鍍:Nickel |

| M44T332538880MHZ | 制造商:MEC 功能描述: |

| M44T3338880MHZ | 制造商:MEC 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。