- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371862 > HMS77C2001 [General Purpose(2) : ADC/ LED/ SCI/ PWM] PDF資料下載

參數(shù)資料

| 型號(hào): | HMS77C2001 |

| 英文描述: | [General Purpose(2) : ADC/ LED/ SCI/ PWM] |

| 中文描述: | [通用(2):藝術(shù)發(fā)展局/發(fā)光/工商/脈寬調(diào)制] |

| 文件頁數(shù): | 29/59頁 |

| 文件大?。?/td> | 660K |

| 代理商: | HMS77C2001 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁當(dāng)前第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁

HMS77C2000/2001

26

Nov. 2002 Ver 1.1

10. I/O PORT

As with any other register, the I/O register can be written

and read under program control. However, read instruc-

tions (e.g.,

MOVF UPIO,W

) always read the I/O pins inde-

pendent of the pin’s input/output modes. On RESET, all I/

O ports are defined as input (inputs are at hi-impedance)

since the I/O control registers are all set.

10.1 UPIO

UPIO is an 8-bit I/O register. Only the low order 6 bits are

used (UP5:UP0). Bits 7 and 6 are unimplemented and read

as '0's. Please note that UP3 is an input only pin. The con-

figuration word can set several I/O’s to alternate func-

tions. When acting as alternate functions the pins will read

as ‘0’ during port read. Pins UP0, UP1, and UP3 can be

configured with weak pull-ups and also with wake-up on

change. The wake-up on change and weak pull-up func-

tions are not pin selectable. If pin 4 is configured as RE-

SET, weak pullup is always on and wake-up on change for

this pin is not enabled.

10.2 TRIS REGISTER

The output driver control register is loaded with the con-

tents of the W register by executing the TRIS f instruction.

A '1' from a TRIS register bit puts the corresponding output

driver in a hi-impedance mode.

A '0' puts the contents of the output data latch on the select-

ed pins, enabling the output buffer. The exceptions are

UP3 which is input only and UP2 which may be controlled

by the option register, see Figure 9-6.

Note:

A read of the ports reads the pins, not the output

data latches. That is, if an output driver on a pin is

enabled and driven high, but the external system is

holding it low, a read of the port will indicate that the

pin is low.

The TRIS registers are “write-only” and are set (output

drivers disabled) upon RESET.

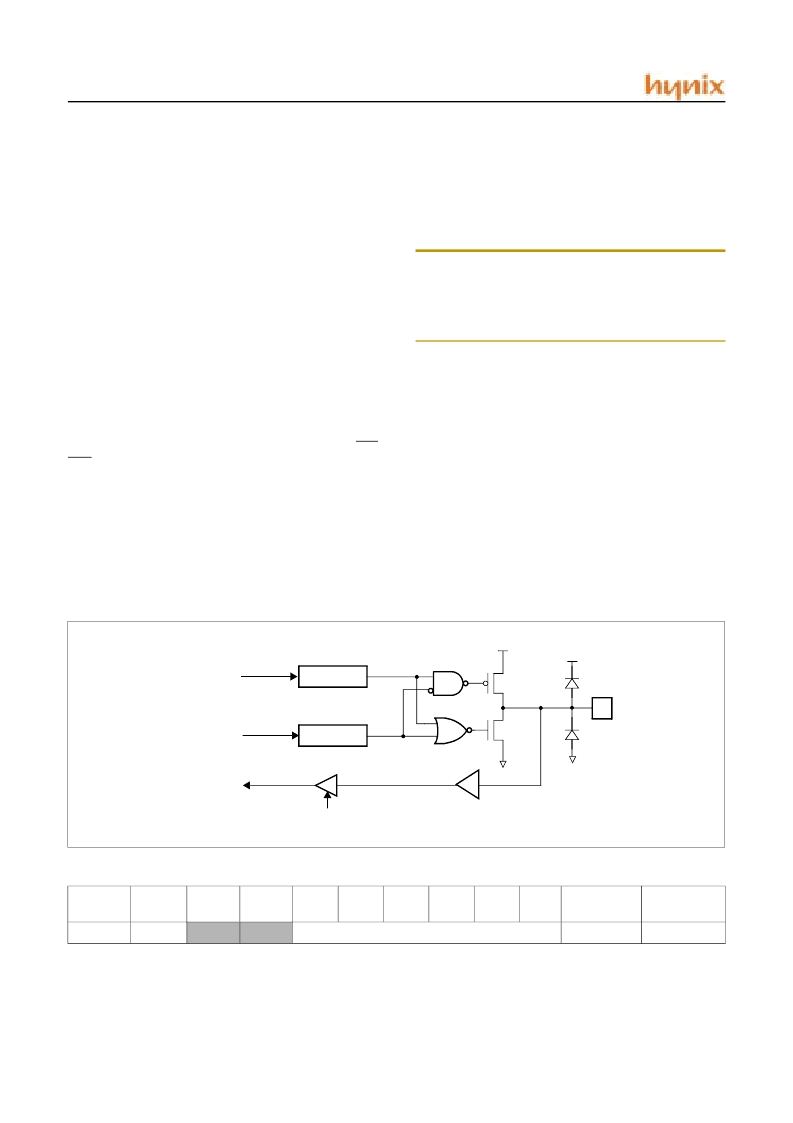

10.3 I/O INTERFACING

The equivalent circuit for an I/O port pin is shown in Fig-

ure 10-1. All port pins, except UP3 which is input only,

may be used for both input and output operations.

For input operations these ports are non-latching. Any in-

put must be present until read by an input instruction e.g.,

MOVF UPIO,W

). The outputs are latched and remain un-

changed until the output latch is rewritten. To use a port pin

as output, the corresponding direction control bit in TRIS

must be cleared (=0). For use as an input, the correspond-

ing TRIS bit must be set. Any I/O pin (except UP3) can be

programmed individually as input or output.

FIGURE 10-1 EQUIVALENT CIRCUIT FOR A SINGLE I/O PIN

Address

Name

Bit7

Bit6

Bit5

Bit4

Bit3

Bit2

Bit1

Bit0

Power-On

Reset

All other

Resets

N/A

TRIS

I/O control registers

--11 1111

--11 1111

TABLE 10-1 SUMMARY OF PORT REGISTERS

Legend: Shaded boxes = unimplemented or unused, - = unimplemented, read as ‘0’, x = unknown, u = unchanged.

Data Bus

Data Bus

Data Bus

Data Reg.

TRIS Reg.

Read

V

DD

V

SS

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HMS81004 | REMOTE CONTROLLER |

| HMS81008 | siHYNIX SEMICONDUCTOR 8-BIT SINGLE-CHIP MICROCONTROLLERS |

| HMS81016 | REMOTE CONTROLLER |

| HMS81020ET | REMOTE CONTROLLER |

| HMS81024 | REMOTE CONTROLLER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HMS81004 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:REMOTE CONTROLLER |

| HMS81004E | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:HYNIX SEMICONDUCTOR 8-BIT SINGLE-CHIP MICROCONTROLLERS |

| HMS81008 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:REMOTE CONTROLLER |

| HMS81008E | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:HYNIX SEMICONDUCTOR 8-BIT SINGLE-CHIP MICROCONTROLLERS |

| HMS81016 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:REMOTE CONTROLLER |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。