- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄366550 > AM79C970 (Advanced Micro Devices, Inc.) PCnetTM-PCI Single-Chip Ethernet Controller for PCI Local Bus PDF資料下載

參數(shù)資料

| 型號: | AM79C970 |

| 廠商: | Advanced Micro Devices, Inc. |

| 英文描述: | PCnetTM-PCI Single-Chip Ethernet Controller for PCI Local Bus |

| 中文描述: | PCnetTM - PCI單芯片以太網(wǎng)控制器的PCI總線 |

| 文件頁數(shù): | 64/168頁 |

| 文件大小: | 943K |

| 代理商: | AM79C970 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁當前第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁

P R E L I M I N A R Y

AMD

1-931

Am79C970

The Vendor Specific Word (VSW) is not implemented by

the PCnet-PCI controller. This particular I/O address is

reserved for customer use and will not be used by future

AMD Ethernet controller products.

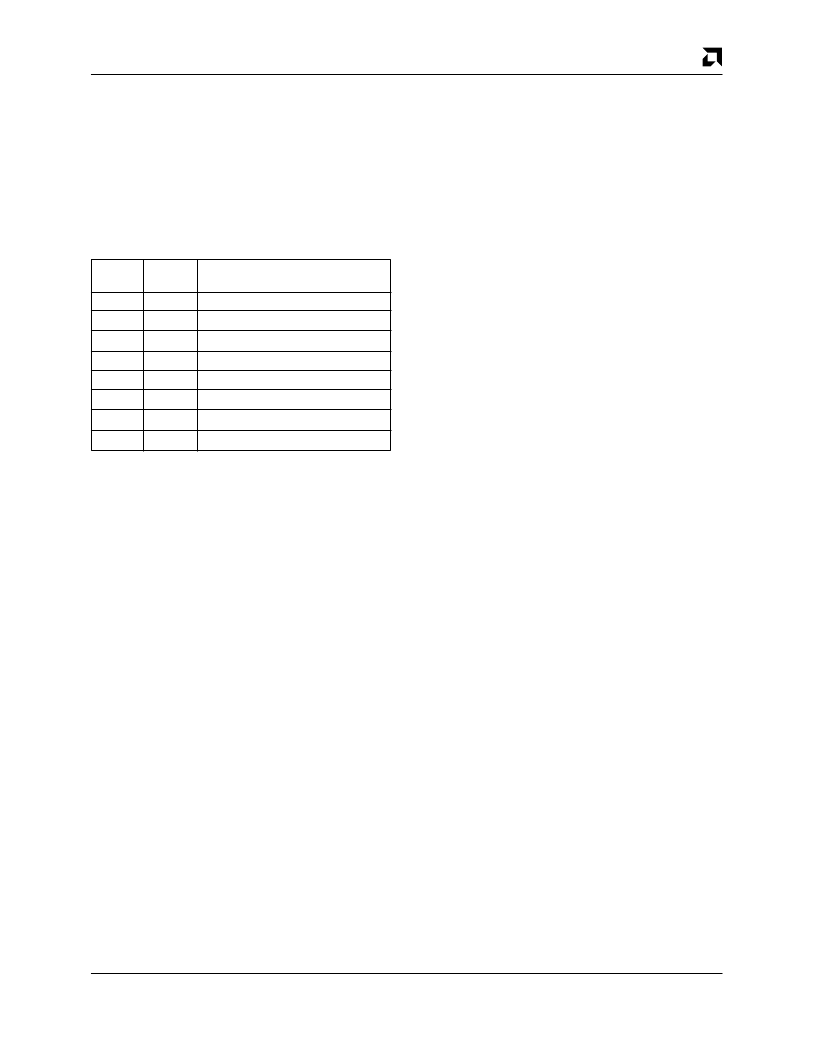

DWIO I/O Resource Map

When the PCnet-PCI controller I/O space is mapped as

Double Word I/O, then all of the resources that are allot-

ted to the PCnet-PCI controller occur on DWORD

boundaries that are offset from the PCnet-PCI controller

I/O base address as shown in the table below:

No. of

Bytes

Offset

Register

0h

4

APROM

4h

4

APROM

8h

4

APROM

Ch

4

APROM

10h

4

RDP

14h

4

RAP (shared by RDP and BDP)

18h

4

Reset Register

1Ch

4

BDP

When PCnet-PCI I/O space is Double Word mapped, all

I/O resources fall on DWORD boundaries. APROM re-

sources are DWORD quantities in DWIO mode. RDP,

RAP and BDP contain only two bytes of valid data; the

other two bytes of these resources are reserved for fu-

ture use. (Note that CSR88 is an exception to this rule.)

The reserved bits must be written as ZEROs, and when

read, are considered undefined.

Accesses to non-doubleword address boundaries are

not allowed while in DWIO mode. (A write access may

cause unexpected reprogramming of the PCnet-PCI

controller control registers; a read access will yield un-

defined values.)

Accesses of less than 4 bytes to any I/O resource are

not allowed while in DWIO mode. (A write access may

cause unexpected reprogramming of the PCnet-PCI

controller control registers; a read access will yield un-

defined values.)

A DWORD write access to the RDP offset of 10h will

automatically program DWIO mode.

Note that in all cases when I/O resource width is defined

as 32 bits, the upper 16 bits of the I/O resource is re-

served and written as ZEROS and read as undefined,

except for the APROM locations and CSR88.

DWIO mode is exited by asserting the

RST

pin. Asser-

tion of S_RESET or setting the STOP bit of CSR0 will

have no effect on the DWIO mode setting.

I/O Space Comments

The following statements apply to both WIO and DWIO

mapping:

The RAP is shared by the RDP and the BDP.

The PCnet-PCI controller does not respond to any ad-

dresses outside of the offset range 0h–17h when DWIO

= 0 or 0h–1Fh when DWIO = 1. I/O offsets 18h through

1Fh are not used by the PCnet-PCI controller when pro-

grammed for DWIO = 0 mode; locations 1Ah through

1Fh are reserved for future AMD use and therefore

should not be implemented by the user if upward com-

patibility to future AMD devices is desired.

Note that APROM accesses do not directly access the

EEPROM, but are redirected to a set of shadow regis-

ters on board the PCnet-PCI controller that contain a

copy of the EEPROM contents that was obtained during

the automatic EEPROM read operation that follows the

H_RESET operation.

PCnet-PCI Controller I/O Base Address

The PCI Configuration Space Base Address register de-

fines what I/O base address the PCnet-PCI controller

uses. This register is typically programmed by the PCI

configuration utility after system power-up. The PCI

configuration utility must also set the IOEN bit in the

COMMAND register to enable I/O accesses to the

PCnet-PCI controller.

The content of the PCnet-PCI I/O Base Address Regis-

ters (BCR16 and BCR17) are ignored.

I/O Register Access

All I/O resources are accessed with similar I/O bus

cycles.

I/O accesses to the PCnet-PCI controller begin with a

valid

FRAME

signal, the C/

BE

[3:0] lines signaling an I/O

read or I/O write operation and an address on the

AD[31:00] lines that falls within the I/O space of the

PCnet-PCI controller. The PCnet-PCI I/O space will be

determined by the Base Address Register in the PCI

Configuration Space.

The PCnet-PCI controller will respond to an access to its

I/O space by asserting the

DEVSEL

signal and eventu-

ally, by asserting the

TRDY

signal.

Typical I/O access times are 6 or 7 clock cycles.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AM79C971VCW | PCnet⑩-FAST Single-Chip Full-Duplex 10/100 Mbps Ethernet Controller for PCI Local Bus |

| AM79C971 | PCnet⑩-FAST Single-Chip Full-Duplex 10/100 Mbps Ethernet Controller for PCI Local Bus |

| AM79C971KCW | IC LOGIC 16211 24-BIT FET BUS SWITCH -40+85C TSSOP-56 35/TUBE |

| AM79C972BKCW | PCnet⑩-FAST+ Enhanced 10/100 Mbps PCI Ethernet Controller with OnNow Support |

| AM79C972BKIW | PCnet⑩-FAST+ Enhanced 10/100 Mbps PCI Ethernet Controller with OnNow Support |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AM79C970A | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:PCnet-PCI II Single-Chip Full-Duplex Ethernet Controller for PCI Local Bus Product |

| AM79C970AKC | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:PCnet-PCI II Single-Chip Full-Duplex Ethernet Controller for PCI Local Bus Product |

| AM79C970AKC\\W | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Advanced Micro Devices 功能描述: |

| AM79C970AKC\W | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復。