- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄366550 > AM79C970 (Advanced Micro Devices, Inc.) PCnetTM-PCI Single-Chip Ethernet Controller for PCI Local Bus PDF資料下載

參數(shù)資料

| 型號(hào): | AM79C970 |

| 廠商: | Advanced Micro Devices, Inc. |

| 英文描述: | PCnetTM-PCI Single-Chip Ethernet Controller for PCI Local Bus |

| 中文描述: | PCnetTM - PCI單芯片以太網(wǎng)控制器的PCI總線 |

| 文件頁數(shù): | 116/168頁 |

| 文件大?。?/td> | 943K |

| 代理商: | AM79C970 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁當(dāng)前第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁

P R E L I M I N A R Y

AMD

1-983

Am79C970

5

BWRITE

Burst Write Enable. When set,

this bit enables Linear Bursting

during memory write accesses,

where Linear Bursting is defined

to mean that only the first transfer

in the current bus arbitration will

contain an address phase. Sub-

sequent transfers will consist of

data phases only. When cleared,

this bit prevents the part from

performing linear bursting during

write accesses. In no case will

the part linearly burst a descriptor

access or an initialization access.

BWRITE should be set to ONE

when the PCnet-PCI controller is

used in a PCI bus application.

The use of burst transfers guar-

antees maximum performance

during memory write operations.

BWRITE is cleared by H_RESET

and is not affected by S_RESET

or STOP.

Reserved location. Written as

ZEROs and read as undefined.

Linear Burst Count. The 3 bit

value in this register sets the up-

per limit for the number of trans-

fer cycles in a Linear Burst. This

limit determines how often the

PCnet-PCI controller will assert a

new

FRAME

signal during linear

burst transfers. Each time that

the interpreted value of LINBC

transfers

is

PCnet-PCI controller will assert a

new

FRAME

signal with a new

valid address. The LINBC value

should contain only one active

bit. LINBC values with more than

one active bit may produce pre-

dictable results, but such values

will not be compatible with future

AMD network controllers.The

LINBC entry is shifted by two bits

before being used by the PCnet-

PCI controller. For example, the

value LINBC[2:0] = 010b is un-

derstood by the PCnet-PCI con-

troller to mean 01000b = 8.

Therefore, the value LINBC[2:0]

= 010b will cause the PCnet-PCI

controller to issue a new

FRAME

every 01000b = 8 transfers. The

PCnet-PCI controller may line-

arly burst fewer than the value

represented by LINBC, due to

other conditions that cause the

burst to end prematurely. There-

fore, LINBC should be regarded

as an upper limit to the length of

linear burst.

4–3

RES

2–0 LINBC[2:0]

reached,

the

Note that linear burst operation

will only begin on certain ad-

dresses. The general rule for lin-

ear burst starting addresses is:

AD[31:00] MOD (LINBC x

16) = 0,

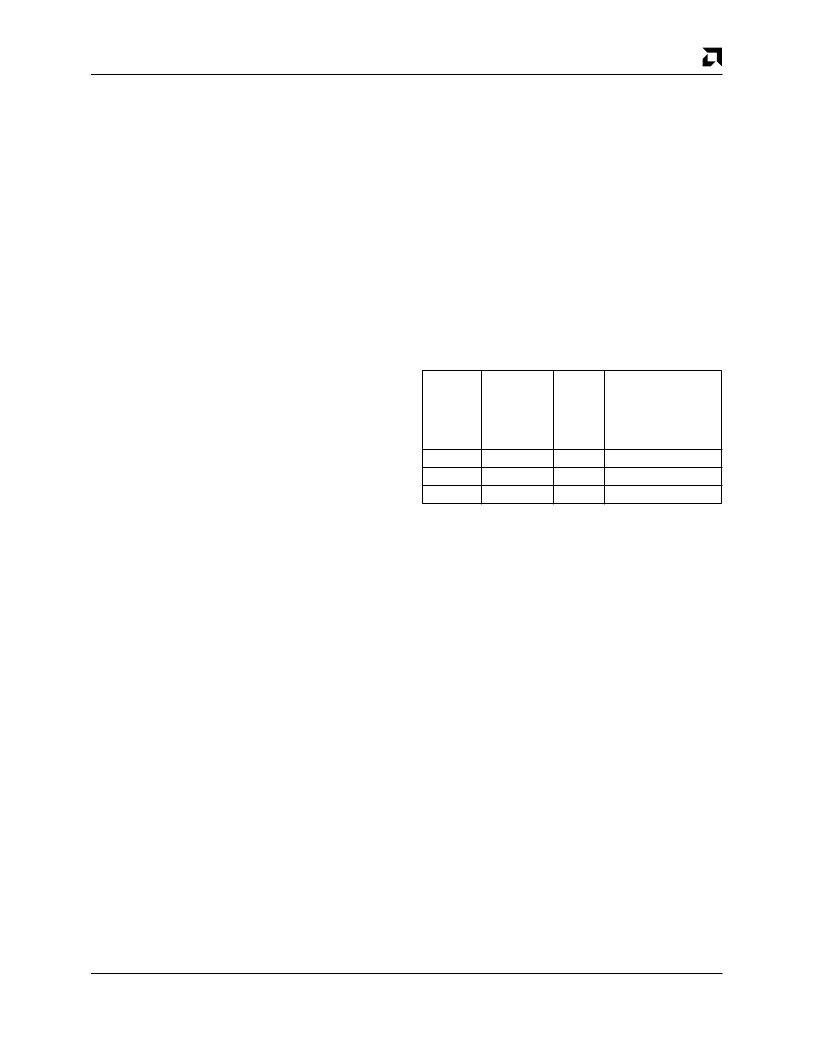

The following table illustrates all

possible starting address values

for all legal LINBC values. Note

that AD[31:06] are don’t care val-

ues for all addresses. Also note

that while AD[1:0] do not physi-

cally exist within a 32 bit system

(the PCnet-PCI controller always

drives AD[1:0] to ZERO during

the address phase to indicate a

linear burst order), they are valid

bits within the buffer pointer field

of descriptor word 0.

Linear Burst

Beginning Addresses

AD[31:6] =

(don’t care)

(AD[5:0] =

(Hex)

LBS =

Linear Burst

Size

(number of

transfers)

Size of

Burst

(bytes)

LINBC[2:0]

1

4

16

00, 10, 20, 30

2

8

32

00, 20

4

16

64

00

There are several events which

may cause early termination of

linear burst. Among those events

are: no more data available for

transfer in either a buffer or in the

FIFO or if either the DMA Trans-

fer Counter (CSR80) or the Bus

Timer Register (CSR82) times

out.

Certain combinations of water-

mark programming and LINBC

programming may create situ-

ations where no linear bursting is

possible, or where the FIFO may

be excessively read or exces-

sively written. Such combina-

tions are declared as illegal.

Combinations of watermark set-

tings and LINBC settings must

obey the following relationship:

watermark (in bytes)

≥

LINBC (in bytes)

Combinations of watermark and

LINBC settings that violate this

rule may cause unexpected

behavior.

LINBC is set to the value of 001b

by H_RESET and is not affected

by S_RESET or STOP. This

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AM79C971VCW | PCnet⑩-FAST Single-Chip Full-Duplex 10/100 Mbps Ethernet Controller for PCI Local Bus |

| AM79C971 | PCnet⑩-FAST Single-Chip Full-Duplex 10/100 Mbps Ethernet Controller for PCI Local Bus |

| AM79C971KCW | IC LOGIC 16211 24-BIT FET BUS SWITCH -40+85C TSSOP-56 35/TUBE |

| AM79C972BKCW | PCnet⑩-FAST+ Enhanced 10/100 Mbps PCI Ethernet Controller with OnNow Support |

| AM79C972BKIW | PCnet⑩-FAST+ Enhanced 10/100 Mbps PCI Ethernet Controller with OnNow Support |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AM79C970A | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:PCnet-PCI II Single-Chip Full-Duplex Ethernet Controller for PCI Local Bus Product |

| AM79C970AKC | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:PCnet-PCI II Single-Chip Full-Duplex Ethernet Controller for PCI Local Bus Product |

| AM79C970AKC\\W | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Advanced Micro Devices 功能描述: |

| AM79C970AKC\W | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。