- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄69018 > MB86860 (FUJITSU LTD) 32-BIT, 200 MHz, RISC PROCESSOR, PBGA352 PDF資料下載

參數(shù)資料

| 型號: | MB86860 |

| 廠商: | FUJITSU LTD |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 32-BIT, 200 MHz, RISC PROCESSOR, PBGA352 |

| 封裝: | PLASTIC, BGA-352 |

| 文件頁數(shù): | 37/70頁 |

| 文件大小: | 1395K |

| 代理商: | MB86860 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁當前第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁

Specifications subject to changes without prior notice

48

MB86860 SPARClite

Cache Area Write Operations

Write operations to cache areas are processed by single transfers in double word units.

DMAC Write Operations

DMAC write operations are performed in 4 X double word burst transfers. (when BMACK# responds to BMREQ#). If

BMACK# does not respond, 4 double word single transfers are performed..

Writes outside of cache areas and other than DMAC

The required number of single transfers is performed as shown in the above table.

5.4.1.3. SPARClite Bus Width

SPARClite Bus Width is set for each CS#.

CS0# Area Bus Width

CS0# is assigned to ROM space. CS0# area bus width is set by the BMODE16# and BMODE32# pins as shown

below. BMODE16# and BMODE32# values are sampled during reset periods.

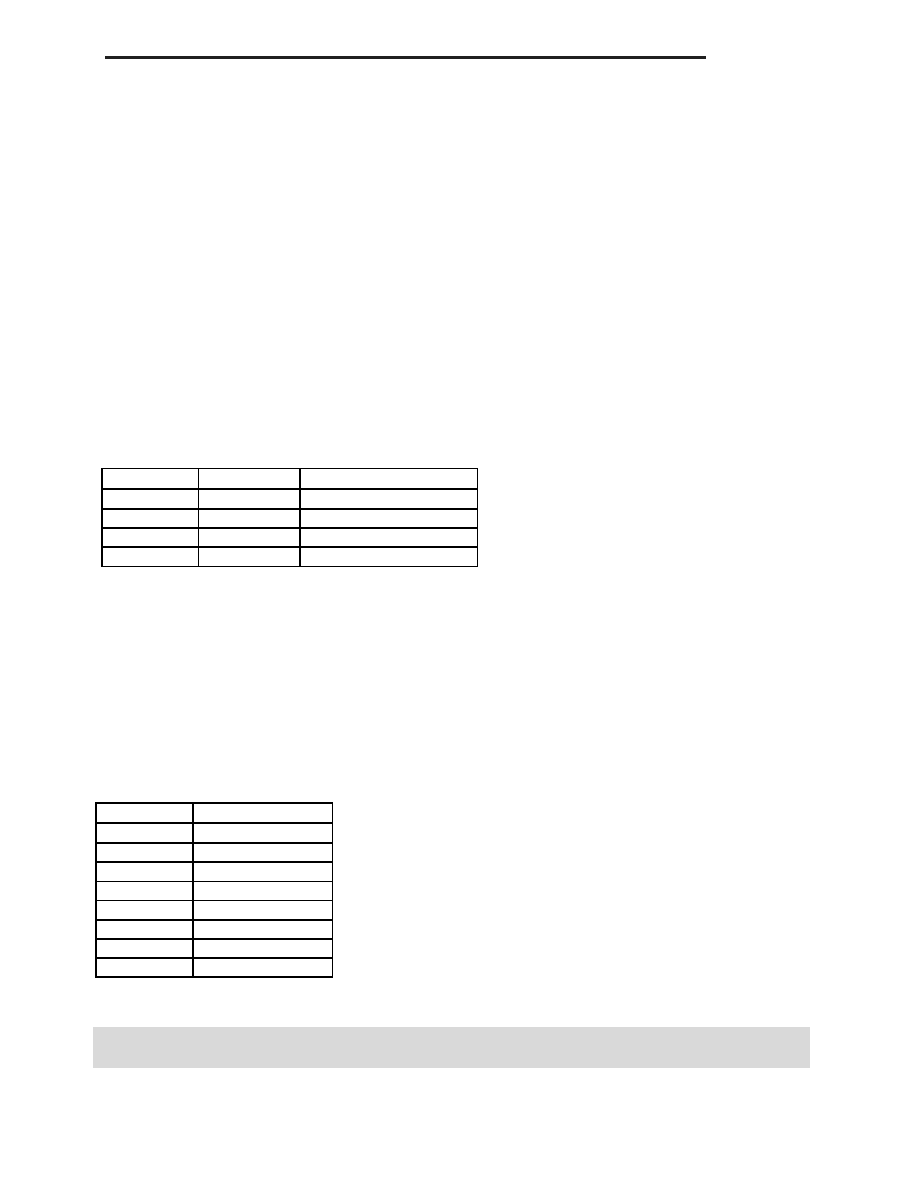

5.4.1.4. Table 5.9 SPARClite Bus Width

BMODE16#

BMODE32#

CS0# Area Bus Width

0

8bit

0

1

16bit

1

0

32bit

1

64bit

CS1#~CS5# Area Bus Width

CS1#~CS5# Area bus Width is set by registers.

[ See explanations of ARSR(Reg.) and AMR(Reg.)]

5.4.1.5. Idle Cycles between Accesses

Idle cycles between accesses are set by settings in the IDCCR (Reg.).

When IDCCR (Reg,) bit0 is 0 and a write operation continues following a read operation, an idle cycle of 1 external

clock is guaranteed from when the read operation READY# is returned to when the write operation AS# is output.

When IDCCR (Reg.) bit0 is 1, the space (idle cycle) from READY# for the CS0# read operation to the next access

(regardless of CS0# and read/write) is guaranteed to be the number of external clocks set to IDCCR (Reg.) bit3~bit1.

Table 5-10 Idle Cycle Settings

IDCCR[3:1]

No. of Idle Cycles

3’b000

1

3’b001

2

3’b010

3

3’b011

4

3’b100

5

3’b101

6

3’b110

7

3’b111

8

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MB86931-20ZF-G | 32-BIT, 20 MHz, RISC MICROCONTROLLER, CQFP256 |

| MB86931-40ZF-G | 32-BIT, 40 MHz, RISC MICROCONTROLLER, CQFP256 |

| MB86933H-20PF-G | 32-BIT, 20 MHz, RISC PROCESSOR, PQFP160 |

| MB86934-60ZF | 32-BIT, 60 MHz, RISC PROCESSOR, CQFP256 |

| MB86936-25/50-PFV-G | 32-BIT, 25 MHz, RISC PROCESSOR, PQFP208 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MB86930-30ZF-G-BND | 制造商:FUJITSU 功能描述: |

| MB86941 | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:Peripheral LSI for SPARClite |

| MB86941PFV | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:Peripheral LSI for SPARClite |

| MB86942 | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:Peripheral LSI for SPARClite |

| MB86942PFV | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:Peripheral LSI for SPARClite |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。