- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379097 > CY7C67200 (Cypress Semiconductor Corp.) EZ-OTG Programmable USB On-The-Go Host/Peripheral Controller(EZ-OTG可編程USB On-The-Go主機/外圍設(shè)備控制器) PDF資料下載

參數(shù)資料

| 型號: | CY7C67200 |

| 廠商: | Cypress Semiconductor Corp. |

| 英文描述: | EZ-OTG Programmable USB On-The-Go Host/Peripheral Controller(EZ-OTG可編程USB On-The-Go主機/外圍設(shè)備控制器) |

| 中文描述: | 的EZ - OTG公司可編程的USB On - The - Go的主機/外設(shè)控制器(的EZ - OTG公司可編程的USB On - The - Go的主機/外圍設(shè)備控制器) |

| 文件頁數(shù): | 66/82頁 |

| 文件大?。?/td> | 1719K |

| 代理商: | CY7C67200 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁當(dāng)前第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁

CY7C67200

Document #: 38-08014 Rev. *F

Page 66 of 82

Reserved

All reserved bits must be written as ‘0’.

8.11.2

UART Status Register [0xC0E2] [R]

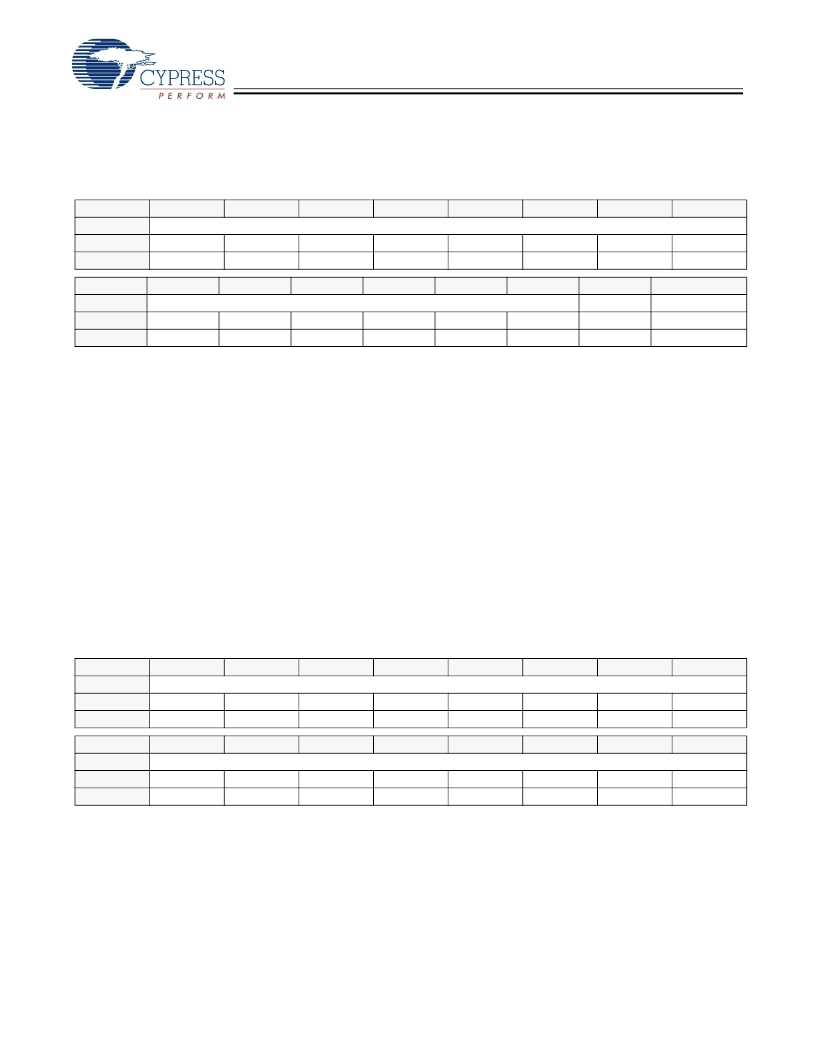

Figure 8-79. UART Status Register

Register Description

The UART Status register is a read only register that indicates the status of the UART buffer.

Receive Full

(Bit 1)

The Receive Full bit indicates whether the receive buffer is full. It can be programmed to interrupt the CPU as interrupt #5 when

the buffer is full. This can be done though the UART bit of the Interrupt Enable register (0xC00E). This bit will automatically be

cleared when data is read from the UART Data register.

1:

Receive buffer full

0:

Receive buffer empty

Transmit Full

(Bit 0)

The Transmit Full bit indicates whether the transmit buffer is full or not. It can be programmed to interrupt the CPU as interrupt

#4 when the buffer is empty. This can be done though the UART bit of the Interrupt Enable register (0xC00E). This bit will

automatically be set to ‘1’ after data is written by EZ-Host to the UART Data register (to be transmitted). This bit will automatically

be cleared to ‘0’ after the data is transmitted.

1:

Transmit buffer full (transmit busy)

0:

Transmit buffer is empty and ready for a new byte of data

8.11.3

UART Data Register [0xC0E4] [R/W]

Figure 8-80. UART Data Register

Register Description

The UART Data register contains data to be transmitted or received from the UART port. Data written to this register will start a

data transmission and also causes the UART Transmit Empty Flag of the UART Status register to set. When data received on

the UART port is read from this register, the UART Receive Full Flag of the UART Status register will get cleared.

Data

(Bits [7:0])

The Data field is where the UART data to be transmitted or received is located

Reserved

All reserved bits must be written as ‘0’.

Bit #

15

14

13

12

11

10

9

8

Field

Reserved...

Read/Write

-

-

-

-

-

-

-

-

Default

0

0

0

0

0

0

0

0

Bit #

7

6

5

4

3

2

1

0

Field

...Reserved

Receive Full

Transmit Full

Read/Write

-

-

-

-

-

-

R

R

Default

0

0

0

0

0

0

0

0

Bit #

15

14

13

12

11

10

9

8

Field

Reserved

Read/Write

-

-

-

-

-

-

-

-

Default

0

0

0

0

0

0

0

Bit #

7

6

5

4

3

2

1

0

Field

Data

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Default

0

0

0

0

0

0

0

0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY7C68320C | EZ-USB AT2LP USB 2.0 to ATA/ATAPI Bridge(EZ-USB AT2LP USB 2.0到ATA/ATAPI橋接器) |

| CY7C68301C | EZ-USB AT2LP USB 2.0 to ATA/ATAPI Bridge(EZ-USB AT2LP USB 2.0到ATA/ATAPI橋接器) |

| CY7C68300C | EZ-USB AT2LP USB 2.0 to ATA/ATAPI Bridge(EZ-USB AT2LP USB 2.0到ATA/ATAPI橋接器) |

| CY7C68321C | EZ-USB AT2LP USB 2.0 to ATA/ATAPI Bridge(EZ-USB AT2LP USB 2.0到ATA/ATAPI橋接器) |

| CY8C20434 | PSoC Mixed-Signal Array(PSoC混合信號陣列) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY7C672001-48BAXI | 功能描述:8位微控制器 -MCU CY7C672001-48BAXI RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時鐘頻率:50 MHz 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

| CY7C672001-48BAXIT | 功能描述:8位微控制器 -MCU CY7C672001-48BAXIT RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時鐘頻率:50 MHz 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

| CY7C67200-48BAXI | 功能描述:USB 接口集成電路 LO PWR OTG IND RoHS:否 制造商:Cypress Semiconductor 產(chǎn)品:USB 2.0 數(shù)據(jù)速率: 接口類型:SPI 工作電源電壓:3.15 V to 3.45 V 工作電源電流: 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:WLCSP-20 |

| CY7C67200-48BAXIT | 功能描述:USB 接口集成電路 LO PWR OTG IND RoHS:否 制造商:Cypress Semiconductor 產(chǎn)品:USB 2.0 數(shù)據(jù)速率: 接口類型:SPI 工作電源電壓:3.15 V to 3.45 V 工作電源電流: 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:WLCSP-20 |

| CY7C67300-100AI | 制造商:Cypress Semiconductor 功能描述:INTERFACE MISC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。