- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376461 > XRT72L74 (Exar Corporation) Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 PDF資料下載

參數(shù)資料

| 型號(hào): | XRT72L74 |

| 廠商: | Exar Corporation |

| 元件分類: | 通信及網(wǎng)絡(luò) |

| 英文描述: | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| 中文描述: | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| 文件頁數(shù): | 28/104頁 |

| 文件大小: | 1301K |

| 代理商: | XRT72L74 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁當(dāng)前第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁

XRT72L74

FOUR CHANNEL, DS3 ATM UNI/CLEAR-CHANNEL FRAMER

REV. P1.0.0

á

PRELIMINARY

28

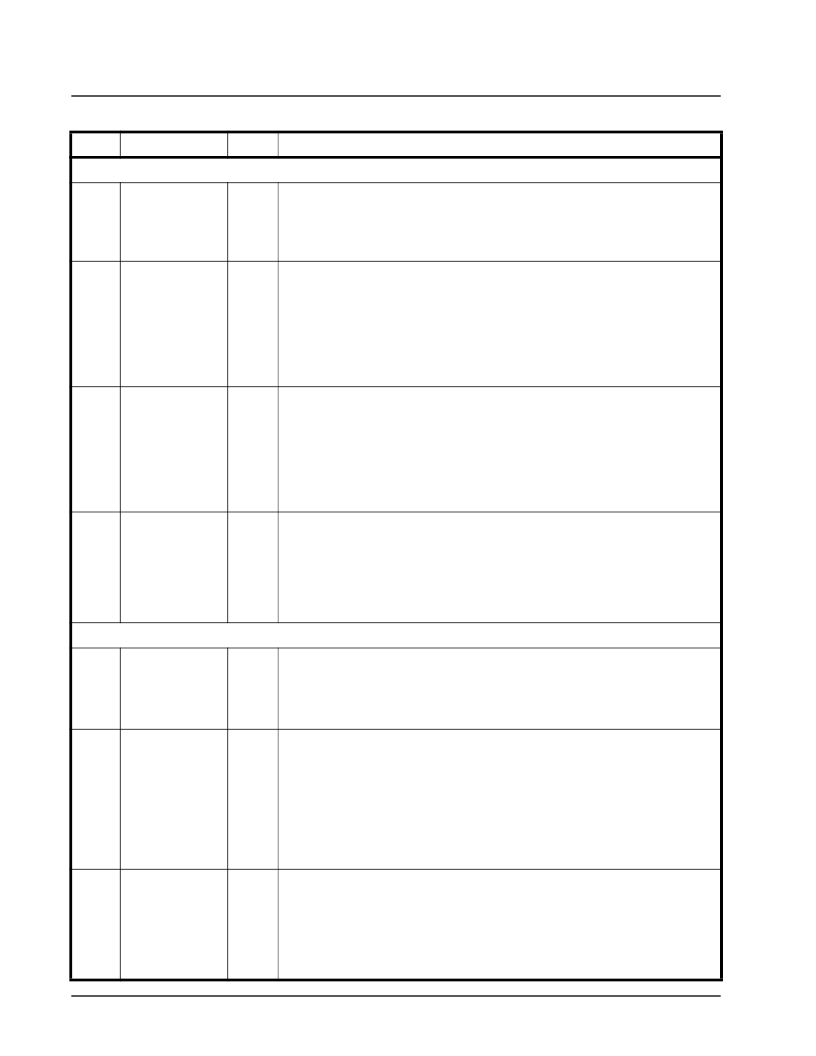

Tx Cell Processor

AC16

AE17

AF17

AF18

TxCellTxed_0

TxCellTxed_1

TxCellTxed_2

TxCellTxed_3

O

Transmit Cell Processor—Cell Transmitted Indicator:

This output pin pulses “High” each time the Transmit Cell Processor transmits a

cell to the Transmit PLCP Processor (or Transmit DS3 Framer).

This output pin is only active if the XRT72L74 has been configured to operate in

the “ATM UNI” Mode.

Transmit GFC Nibble-Field Serial Input Port:

This signal, along with TxGFCClk and TxGFCMSB combine to function as the

“Transmit GFC Nibble-field” serial input port. The user will specify the value of the

GFC field, within a given ATM cell, by serial transmitting its four bit value into this

input. Each of these four bits will be clocked into the UNI via rising edge of the

TxGFCClk clock output signal.

N

OTE

:

The user should tie this input pin to “GND” whenever the XRT72L74 has

been configured to operate in the “Clear-Channel-Framer” Mode.

Transmit GFC Nibble Field Serial Input Port Clock:

This signal, along with TxGFC, and TxGFCMSB combine to function as the “Trans-

mit GFC Nibble-field” serial input port. The “Transmit GFC Nibble-field” serial input

port uses this output clock signal to sample the values applied to the TxGFC pin,

on its rising edge. This pin will provide four rising edges for each cell being trans-

mitted.

N

OTE

:

This output pin is only active whenever the XRT72L74 has been configured

to operate in the “ATM UNI” Mode.

Transmit GFC Nibble-Field Serial Input Port—MSB Indicator:

This signal, along with TxGFC and TxGFCClk combine to function as the “Transmit

GFC Nibble Field” serial input port. This output signal will pulse “High” when the

MSB (most significant bit) of the GFC Nibble (for a given cell) is expected at the

TxGFC input pin.

N

OTE

:

This output pin is only active whenever the XRT72L74 has been configured

to operate in the “ATM UNI” Mode.

AD7

AE7

AF7

AE8

TxGFC_0

TxGFC_1

TxGFC_2

TxGFC_3

I

AF5

AE6

AF6

AC6

TxGFCClk_0

TxGFCClk_1

TxGFCClk_2

TxGFCClk_3

O

AF8

AE9

AF9

AE10

TxGFCMSB_0

TxGFCMSB_1

TxGFCMSB_2

TxGFCMSB_3

O

Rx Cell Processor

AD19

AE19

AF19

AD20

RxCellRxed_0

RxCellRxed_1

RxCellRxed_2

RxCellRxed_3

O

Receive Cell Processor—Cell Received Indicator:

This output pin pulses “High” each time the Receive Cell Processor receives a new

cell from the Receive PLCP Processor or the Receive DS3 Framer.

N

OTE

:

This output pin is only active if the XRT72L74 has been configured to oper-

ate in the “ATM UNI” Mode.

Receive GFC Nibble Field Serial Output pin:

This pin, along with the RxGFCClk and the RxGFCMSB pins form the “Receive

GFC Nibble-Field” serial output port. This pin will serially output the contents of the

GFC Nibble field of each cell that is processed through the Receive Cell Proces-

sor. This data is serially clocked out of this pin on the rising edge of the RxGFCClk

signal. The Most Significant Bit (MSB) of each GFC value is designated by a pulse

at the RxGFCMSB output pin.

N

OTE

:

This output pin is only active if the XRT72L74 has been configured to oper-

ate in the “ATM UNI” Mode.

AF23

AF25

AD26

AC25

RxGFC_0

RxGFC_1

RxGFC_2

RxGFC_3

O

Y24

Y25

Y26

Y23

RxGFCClk_0

RxGFCClk_1

RxGFCClk_2

RxGFCClk_3

O

Received GFC Nibble Serial Output Port Clock Signal:

This output pin functions as a part of the “Receive GFC Nibble-Field” Serial Output

Port; also consisting of the RxGFC and RxGFCMSB pins. This pin provides a

clock pulse which allows external circuitry to latch in the GFC Nibble-Data via the

RxGFC output pin.

N

OTE

:

This output pin is only active if the XRT72L74 has been configured to oper-

ate in the “ATM UNI” Mode.

PIN DESCRIPTIONS

P

IN

#

N

AME

T

YPE

D

ESCRIPTION

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XRT7300IV | E3/DS3/STS-1 LINE INTERFACE UNIT |

| XRT7300 | E3/DS3/STS-1 LINE INTERFACE UNIT |

| XRT7302 | 2 Channel E3/DS3/STS-1 Line Interface Unit(2通道 E3/DS3/STS-1線接口單元) |

| XRT73L02M | TWO CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT |

| XRT73L02MIV | TWO CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XRT72L74IB | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Telecommunication IC |

| XRT7300 | 制造商:EXAR 制造商全稱:EXAR 功能描述:E3/DS3/STS-1 LINE INTERFACE UNIT |

| XRT7300ES | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| XRT7300IV | 功能描述:外圍驅(qū)動(dòng)器與原件 - PCI . . RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| XRT7300IV-F | 功能描述:外圍驅(qū)動(dòng)器與原件 - PCI RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。