- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385949 > TSB81BA3I (Texas Instruments, Inc.) IEEE 1394b THREE-PORT CABLE TRANSCEIVER/ARBITER PDF資料下載

參數(shù)資料

| 型號: | TSB81BA3I |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | IEEE 1394b THREE-PORT CABLE TRANSCEIVER/ARBITER |

| 中文描述: | 的IEEE 1394b三端口電纜收發(fā)器/仲裁者 |

| 文件頁數(shù): | 39/57頁 |

| 文件大小: | 810K |

| 代理商: | TSB81BA3I |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁當(dāng)前第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁

SLLS559B DECEMBER 2002 REVISED OCTOBER 2003

39

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

PRINCIPLES OF OPERATION (1394a2000 INTERFACE)

interface reset and disable (continued)

The LLC requests that the interface be reset by deasserting the LPS signal and terminating all bus and request

activity. When the PHY observes that LPS has been deasserted for T

LPS_RESET

, it resets the interface. When

the interface is in the reset state, the PHY sets its CTL and D outputs in the logic 0 state and ignores any activity

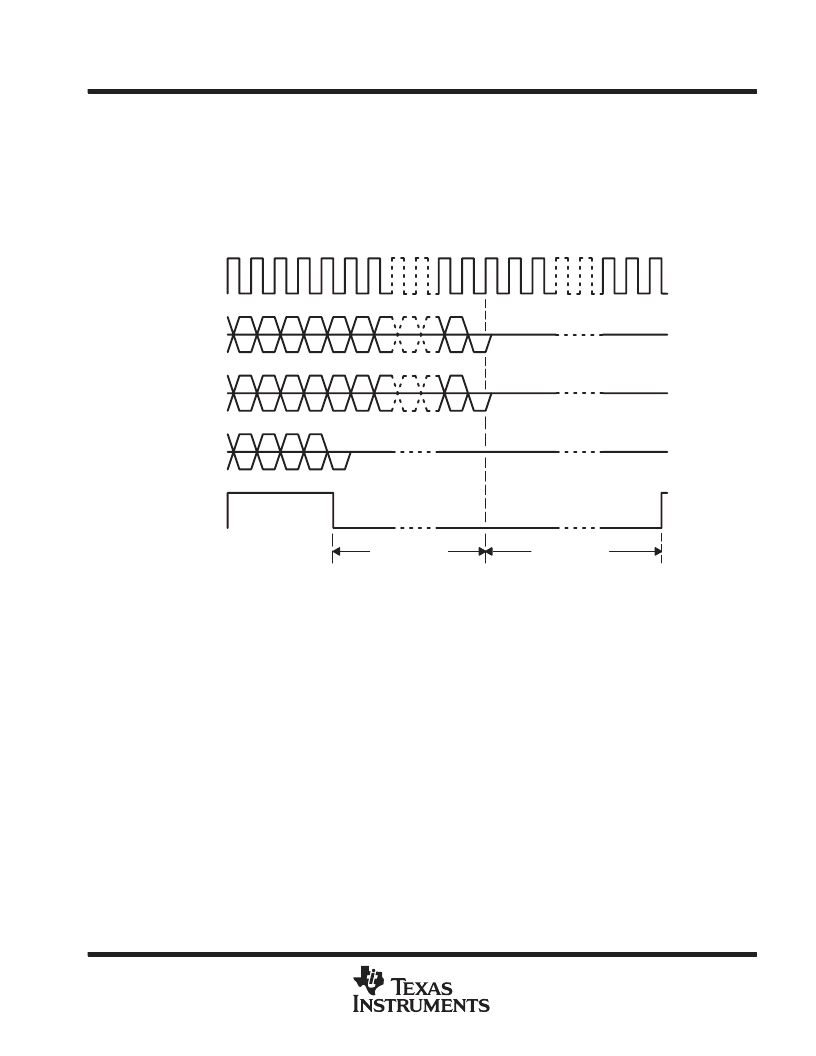

on the LREQ signal. Figure 17 shows the timing for interface reset.

PCLK

(a)

(c)

(b)

CTL0, CTL1

D0 D7

LREQ

LPS

(d)

TLPS_RESET

TRESTORE

Figure 17. Interface Reset

The sequence of events for resetting the PHY-LLC interface is as follows:

(a) Normal operation. Interface is operating normally, with LPS asserted, PCLK active, status and packet data

reception and transmission via the CTL and D lines, and request activity via the LREQ line. In the above

diagram, the LPS signal is shown as a nonpulsed level signal. However, it is permissible to use a pulsed

signal for LPS in a direct connection between the PHY and LLC; a pulsed signal is required when using an

isolation barrier.

(b) LPS deasserted. The LLC deasserts the LPS signal and, within 1.0

μ

s, terminates any request or interface

bus activity, places its CTL and D outputs into a high-impedance state, and drives its LREQ output low.

(c) Interface reset. After T

LPS_RESET

time, the PHY determines that LPS is inactive, terminates any interface

bus activity, and drives its CTL and D outputs low. The PHY-LLC interface is now in the reset state.

(d) Interface restored. After the minimum T

RESTORE

time, the LLC may again assert LPS active. When LPS

is asserted, the interface is initialized as described below.

If the LLC continues to keep the LPS signal deasserted, it then requests that the interface be disabled. The PHY

disables the interface when it observes that LPS has been deasserted for T

LPS_DISABLE

. When the interface

is disabled, the PHY sets its CTL and D outputs as stated above for interface reset, but also stops PCLK activity.

The interface is also placed into the disabled condition upon a hardware reset of the PHY. Figure 18 shows the

timing for the interface disable.

When the interface is disabled, the PHY enters a low-power state if none of its ports are active.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TSE-0155-32S-P1-3 | SINGLE MODE SINGLE FIBER TRANSCEIVER |

| TSL230 | PROGRAMMABLE LIGHT-TO-FREQUENCY CONVERTERS |

| TSL235(中文) | Programmable Light-To-Frequency Converter(光頻轉(zhuǎn)換器) |

| TSL245(中文) | IR Light-To-Frequency Converter(紅外光頻轉(zhuǎn)換器) |

| TSL250(中文) | Light-To-Voltage Converter(光壓轉(zhuǎn)換器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TSB81BA3IPFP | 功能描述:射頻收發(fā)器 s800 3-Port Cable Xcvr/Arbiter RoHS:否 制造商:Atmel 頻率范圍:2322 MHz to 2527 MHz 最大數(shù)據(jù)速率:2000 Kbps 調(diào)制格式:OQPSK 輸出功率:4 dBm 類型: 工作電源電壓:1.8 V to 3.6 V 最大工作溫度:+ 85 C 接口類型:SPI 封裝 / 箱體:QFN-32 封裝:Tray |

| TSB81BA3IPFPEP | 功能描述:射頻收發(fā)器 Mil Enh 3-Port Cable Xcvr/Arbiter RoHS:否 制造商:Atmel 頻率范圍:2322 MHz to 2527 MHz 最大數(shù)據(jù)速率:2000 Kbps 調(diào)制格式:OQPSK 輸出功率:4 dBm 類型: 工作電源電壓:1.8 V to 3.6 V 最大工作溫度:+ 85 C 接口類型:SPI 封裝 / 箱體:QFN-32 封裝:Tray |

| TSB81BA3PFP | 功能描述:射頻收發(fā)器 s800 3-Port Cable Xcvr/Arbiter RoHS:否 制造商:Atmel 頻率范圍:2322 MHz to 2527 MHz 最大數(shù)據(jù)速率:2000 Kbps 調(diào)制格式:OQPSK 輸出功率:4 dBm 類型: 工作電源電壓:1.8 V to 3.6 V 最大工作溫度:+ 85 C 接口類型:SPI 封裝 / 箱體:QFN-32 封裝:Tray |

| TSB81BA3PFPG4 | 功能描述:射頻收發(fā)器 s800 3-Port Cable Xcvr/Arbiter RoHS:否 制造商:Atmel 頻率范圍:2322 MHz to 2527 MHz 最大數(shù)據(jù)速率:2000 Kbps 調(diào)制格式:OQPSK 輸出功率:4 dBm 類型: 工作電源電壓:1.8 V to 3.6 V 最大工作溫度:+ 85 C 接口類型:SPI 封裝 / 箱體:QFN-32 封裝:Tray |

| TSB82AA2 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:1394b OHCI-LYNX CONTROLLER |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。