- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371186 > TLIU04C1 (Lineage Power) Quad T1/E1 Line Interface(四T1/E1線接口) PDF資料下載

參數(shù)資料

| 型號: | TLIU04C1 |

| 廠商: | Lineage Power |

| 英文描述: | Quad T1/E1 Line Interface(四T1/E1線接口) |

| 中文描述: | 四T1/E1線路接口(四個T1/E1線接口) |

| 文件頁數(shù): | 11/100頁 |

| 文件大?。?/td> | 1321K |

| 代理商: | TLIU04C1 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁當前第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁

Advance Data Sheet, Rev. 2

April 1999

TLIU04C1 Quad T1/E1 Line Interface

11

Lucent Technologies Inc.

Microprocessor Mode

(continued)

Pin Information

(continued)

Table 1. Pin Descriptions

(continued)

* I = input, O = output, I

u

indicates an input with internal pull-up; I

d

indicates an input with internal pull-down, P = power. Resistance value of all

internal pull-ups or pull-downs is 50 k

, unless otherwise specified.

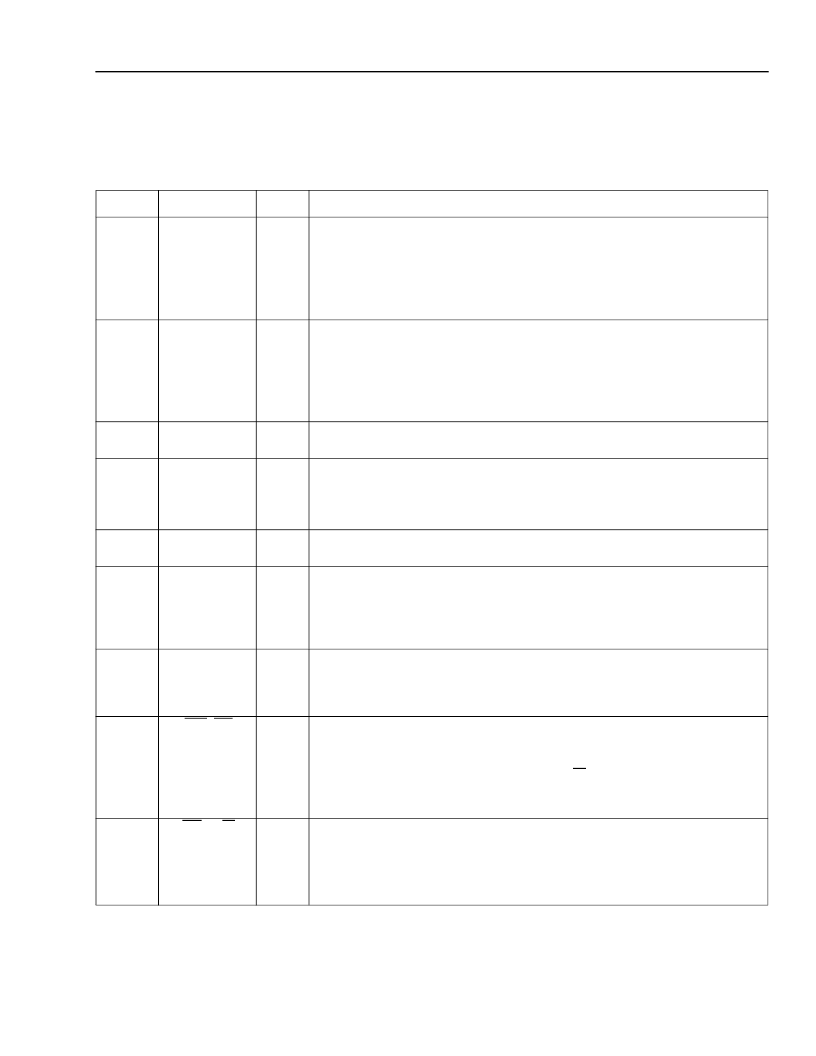

Pin

Symbol

Type

*

Name/Description

138, 19,

66, 91

RPD/RDATA

[1—4]

O

Receive Positive Data.

When in dual-rail (DUAL = 1: register 5, bit 4) clock

recovery mode (CDR = 1: register 5, bit 0), this signal is the received positive

NRZ data to the terminal equipment. When in data slicing mode (CDR = 0),

this signal is the raw sliced positive data of the front end.

Receive Data.

When in single-rail (DUAL = 0: register 5, bit 4) clock recovery

mode (CDR = 1: register 5, bit 0), this signal is the received NRZ data.

Receive Clock.

In clock recovery mode (CDR = 1: register 5, bit 0), this

signal is the recovered receive clock for the terminal equipment. The duty

cycle of RCLK is 50% ± 5%.

Analog Loss of Signal.

In data slicing mode (CDR = 0: register 5, bit 0), this

signal is asserted high to indicate low amplitude receive data at the RTIP/

RRING inputs.

Transmit Negative Data.

This signal is the transmit negative NRZ data from

the terminal equipment.

Transmit Positive Data.

When in dual-rail mode (DUAL = 1: register 5, bit 4),

this signal is the transmit positive NRZ data from the terminal equipment.

Transmit Data.

When in single-rail mode (DUAL = 0: register 5, bit 4), this

signal is the transmit NRZ data from the terminal equipment.

Transmit Clock.

DS1 (1.544 MHz ± 32 ppm) or CEPT (2.048 MHz ±

50 ppm) clock signal from the terminal equipment.

Microprocessor Mode.

When MPMODE = 1, the device uses the address

latch enable type microprocessor read/write protocol with separate read and

write controls. Setting MPMODE = 0 allows the device to use the address

strobe type microprocessor read/write protocol with a separate data strobe

and a combined read/write control.

Microprocessor Multiplex Mode.

Setting MPMUX = 1 allows the

microprocessor interface to accept multiplexed address and data signals.

Setting MPMUX = 0 allows the microprocessor interface to accept

demultiplexed (separate) address and data signals.

Write (Active-Low).

If MPMODE = 1 (pin 110), this pin is asserted low by the

microprocessor to initiate a write cycle.

Data Strobe (Active-Low).

If MPMODE = 0 (pin 21), this pin becomes the

data strobe for the microprocessor. When R/W = 0 (pin 111) initiating a write,

a low applied to this pin latches the signal on the data bus into internal

registers.

Read (Active-Low).

If MPMODE = 1 (pin 110), this pin is asserted low by the

microprocessor to initiate a read cycle.

Read/Write.

If MPMODE = 0 (pin 110), this pin is asserted high by the

microprocessor to initiate a read cycle or asserted low to initiate a write

cycle.

139, 18,

67, 90

RCLK/ALOS

[1—4]

O

140, 17,

68, 89

141, 16,

69, 88

TND[1—4]

I

TPD/TDATA

[1—4]

I

142, 15,

70, 87

110

TCLK[1—4]

I

MPMODE

I

108

MPMUX

I

107

WR_DS

I

111

RD_R/W

I

相關PDF資料 |

PDF描述 |

|---|---|

| TLV3011AIDBVR | Nanopower, 1.8V, SOT23 Comparator with Voltage Reference |

| TLV349x | CAPACITOR, CLASS Y2 1.0NFCAPACITOR, CLASS Y2 1.0NF; Capacitance:1nF; Voltage rating, AC:250V; Voltage rating, DC:2500V; Capacitor dielectric type:Polypropylene; Series:B81122; Tolerance, +:20%; Tolerance, -:20%; Temp, op. |

| TLV3011AIDBVT | Nanopower, 1.8V, SOT23 Comparator with Voltage Reference |

| TLV3011AIDCKR | Nanopower, 1.8V, SOT23 Comparator with Voltage Reference |

| TLV3011AIDCKT | Nanopower, 1.8V, SOT23 Comparator with Voltage Reference |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| TLIXF30001 | 制造商:GIGA 功能描述: |

| TLIXF30003 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| TLIXF30007-852838 | 制造商:Cortina Systems Inc 功能描述: |

| TLIXF30009-865852 | 功能描述:IC OPT TRANSPORT PROC 868-TBGA RoHS:是 類別:集成電路 (IC) >> 接口 - 電信 系列:- 產品培訓模塊:Lead (SnPb) Finish for COTS 產品變化通告:Product Discontinuation 06/Feb/2012 標準包裝:750 系列:* |

| TLIXF30010 | 制造商:Intel 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復。