- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369950 > PCI1620GHK Controller Miscellaneous - Datasheet Reference PDF資料下載

參數(shù)資料

| 型號(hào): | PCI1620GHK |

| 英文描述: | Controller Miscellaneous - Datasheet Reference |

| 中文描述: | 控制器雜項(xiàng)-數(shù)據(jù)表參考 |

| 文件頁(yè)數(shù): | 86/164頁(yè) |

| 文件大?。?/td> | 720K |

| 代理商: | PCI1620GHK |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)當(dāng)前第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)第158頁(yè)第159頁(yè)第160頁(yè)第161頁(yè)第162頁(yè)第163頁(yè)第164頁(yè)

4

–

18

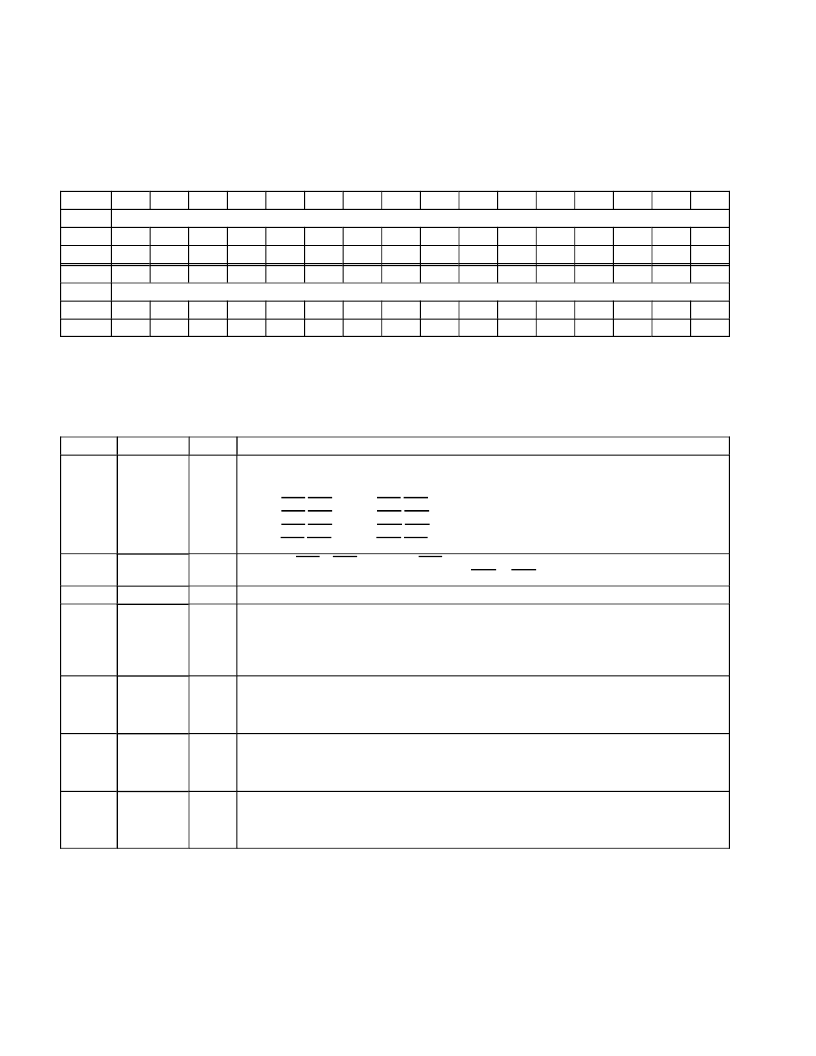

4.31 System Control Register

System-level initializations are performed through programming this doubleword register. Some of the bits are global

in nature and should be accessed only through function 0. See Table 4

–

7 for a complete description of the register

contents.

Bit

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

Name

System control

Type

RW

RW

RW

RW

RW

RW

RW

RW

R

RW

RW

RW

RW

RW

RW

RW

Default

0

0

0

0

0

0

0

0

0

1

0

0

0

1

0

0

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

System control

Type

RW

RW

R

R

R

R

R

R

R

RW

RW

RW

RW

R

RW

RW

Default

1

0

0

1

0

0

0

0

0

1

1

0

0

0

0

0

Register:

Offset:

Type:

Default:

System control

80h (Functions 0, 1)

Read-only, Read/Write

0044 9060h

Table 4

–

7. System Control Register Description

BIT

SIGNAL

TYPE

FUNCTION

31

–

30

SER_STEP

RW

Serial input stepping. In serial PCI interrupt mode, these bits are used to configure the serial stream PCI

interrupt frames, and can be used to accomplish an even distribution of interrupts signaled on the four PCI

interrupt slots.

00 = INTA/INTB signal in INTA/INTB slots (default)

01 = INTA/INTB signal in INTB/INTC slots

10 = INTA/INTB signal in INTC/INTD slots

11 = INTA/INTB signal in INTD/INTA slots

29

INTRTIE

RW

This bit ties INTA to INTB internally (to INTA), and reports this through the interrupt pin register (PCI offset

3Dh, see Section 4.24). This bit has no effect on INTC or INTD.

28

RSVD

R

Reserved. Bit 28 returns 0 when read.

27

P2CCLK

RW

P2C power switch CLOCK. This bit determines whether the CLOCK terminal (PDV 154 or GHK F15) is

an input that requires an external clock source or if this terminal is an output that uses the internal oscillator.

Bit 27 can be set to enable the PCI1620 to generate and drive CLOCK from the PCI clock.

0 = CLOCK provided externally, input to PCI1620 (default)

1 = CLOCK generated by PCI clock and driven by PCI1620

26

SMIROUTE

RW

SMI interrupt routing. This bit is shared between functions 0 and 1, and selects whether IRQ2 or CSC is

signaled when a write occurs to power a PC Card socket.

0 = PC Card power change interrupts are routed to IRQ2 (default).

1 = A CSC interrupt is generated on PC Card power changes.

25

SMISTATUS

RW

SMI interrupt status. This socket-dependent bit is set when a write occurs to set the socket power, and

the SMIENB bit is set. Writing a 1 to this bit clears the status.

0 = SMI interrupt is signaled.

1 = SMI interrupt is not signaled.

24

SMIENB

RW

SMI interrupt mode enable. When this bit is set, the SMI interrupt signaling generates an interrupt when

a write to the socket power control occurs. This bit is shared and defaults to 0 (disabled).

0 = SMI interrupt mode is disabled (default).

1 = SMI interrupt mode is enabled.

These bits are global in nature and should be accessed only through function 0.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PCI1620PDV | Controller Miscellaneous - Datasheet Reference |

| PCI2050A | 32-Bit. 66MHz. 9-Master PCI-to-PCI Bridge |

| PCI2050GHK | BUS CONTROLLER |

| PCI2050PDV | BUS CONTROLLER |

| PCI9054AB50BI | Interface IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PCI1620PDV | 功能描述:外圍驅(qū)動(dòng)器與原件 - PCI PC Card Flash & Smart Card Cntrlr RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| PCI-1620U | 制造商:ADVANTECH 制造商全稱:Advantech Co., Ltd. 功能描述:8-port RS-232 PCI Communication Card, with Surge Protection |

| PCI1620ZHK | 功能描述:外圍驅(qū)動(dòng)器與原件 - PCI PC Card Flash & Smart Card Cntrlr RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| PCI-1622A-BE | 制造商:Advantech Co Ltd 功能描述:8PORT RS-422/485 PCI COM CARD - Trays 制造商:Advantech Co Ltd 功能描述:8-port RS-422/485 UPCI COMM card |

| PCI-1622CU | 制造商:ADVANTECH 制造商全稱:Advantech Co., Ltd. 功能描述:8-port RS-422/485 Universal PCI Communication Card with Isolation & EFT Protection |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。