6

–

4

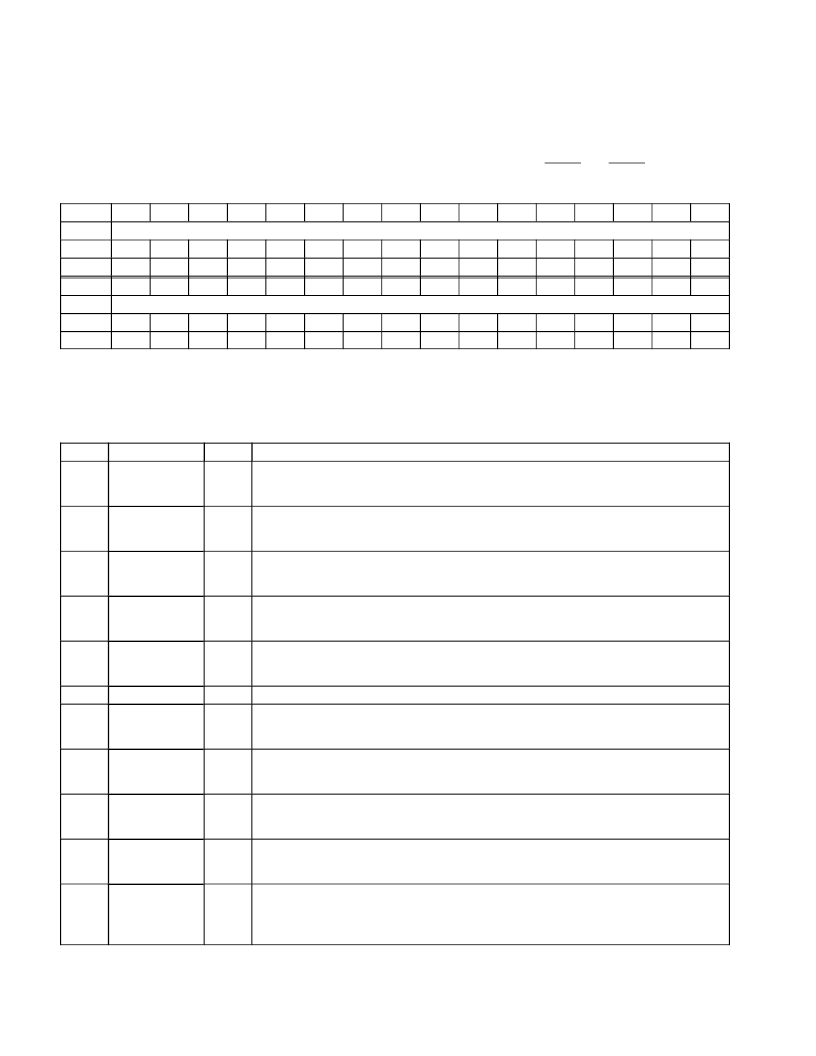

6.3

Socket Present State Register

This register reports information about the socket interface. Writes to the socket force event register (offset 0Ch, see

Section 6.4), as well as general socket interface status, are reflected here. Information about PC Card V

CC

support

and card type is only updated at each insertion. Also note that the PCI1620 uses the CCD1 and CCD2 signals during

card identification, and changes on these signals during this operation are not reflected in this register.

Bit

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

Name

Socket present state

Type

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

Default

0

0

1

1

0

0

0

0

0

0

0

0

0

0

0

0

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

Socket present state

Type

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

Default

0

0

0

0

0

0

0

0

0

X

0

0

0

X

X

X

Register:

Offset:

Type:

Default:

Socket present state

CardBus Socket Address + 08h

Read-only

3000 00XXh

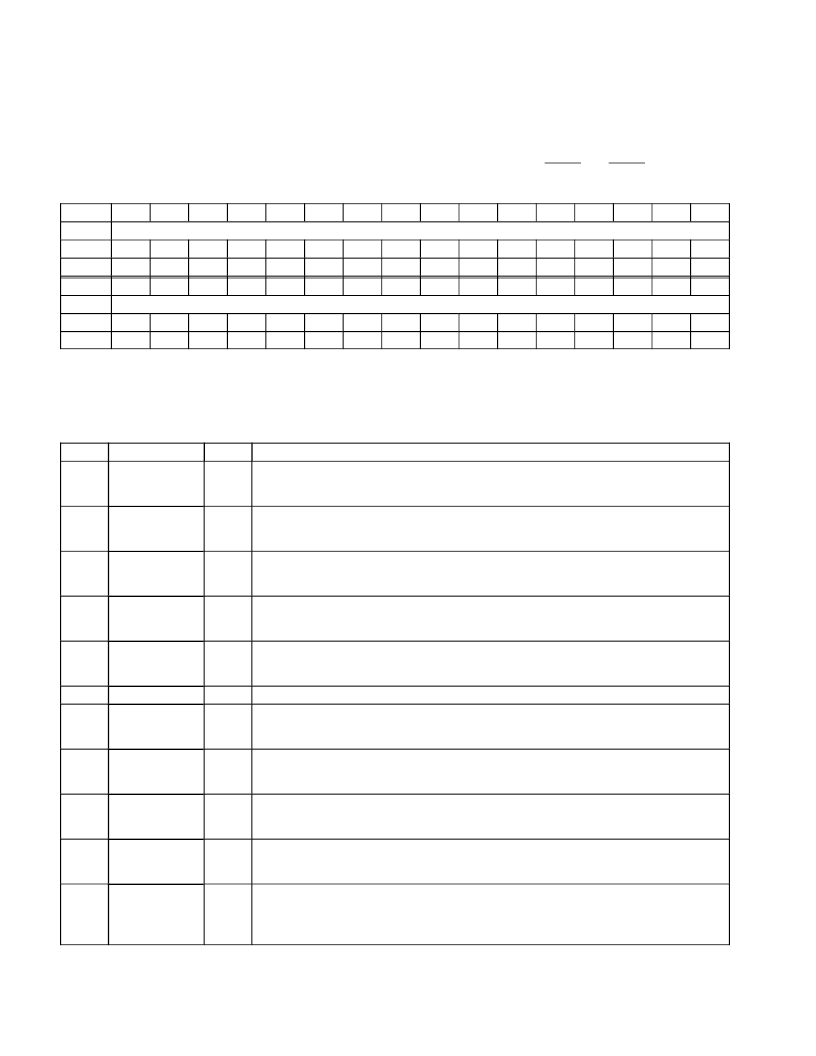

Table 6

–

4. Socket Present State Register Description

BIT

SIGNAL

TYPE

FUNCTION

31

YVSOCKET

R

YV socket. This bit indicates whether or not the socket can supply VCC = Y.Y V to PC Cards. The

PCI1620 does not support Y.Y-V VCC; therefore, this bit is always reset unless overridden by the socket

force event register (offset 0Ch, see Section 6.4). This bit defaults to 0.

30

XVSOCKET

R

XV socket. This bit indicates whether or not the socket can supply VCC = X.X V to PC Cards. The

PCI1620 does not support X.X-V VCC; therefore, this bit is always reset unless overridden by the socket

force event register (offset 0Ch, see Section 6.4). This bit defaults to 0.

29

3VSOCKET

R

3-V socket. This bit indicates whether or not the socket can supply VCC = 3.3 Vdc to PC Cards. The

PCI1620 does support 3.3-V VCC; therefore, this bit is always set unless overridden by the socket force

event register (offset 0Ch, see Section 6.4).

28

5VSOCKET

R

5-V socket. This bit indicates whether or not the socket can supply VCC = 5 Vdc to PC Cards. The

PCI1620 does support 5-V VCC; therefore, this bit is always set unless overridden by bit 6 0f the device

control register (PCI offset 92h, see Section 4.41).

27

ZVSUPPORT

R

Zoomed video support. This bit indicates whether or not the socket has support for zoomed video.

0 = ZV support disabled

1 = ZV support enabled

26

–

14

RSVD

R

These bits return 0s when read.

13

YVCARD

R

YV card. This bit indicates whether or not the PC Card inserted in the socket supports VCC = Y.Y Vdc.

This bit can be set by writing a 1 to the corresponding bit in the socket force event register (offset 0Ch,

see Section 6.4).

12

XVCARD

R

XV card. This bit indicates whether or not the PC Card inserted in the socket supports VCC = X.X Vdc.

This bit can be set by writing a 1 to the corresponding bit in the socket force event register (offset 0Ch,

see Section 6.4).

11

3VCARD

R

3-V card. This bit indicates whether or not the PC Card inserted in the socket supports VCC = 3.3 Vdc.

This bit can be set by writing a 1 to the corresponding bit in the socket force event register (offset 0Ch,

see Section 6.4).

10

5VCARD

R

5-V card. This bit indicates whether or not the PC Card inserted in the socket supports VCC = 5 Vdc.

This bit can be set by writing a 1 to the corresponding bit in the socket force event register (offset 0Ch,

see Section 6.4).

9

BADVCCREQ

R

Bad VCC request. This bit indicates that the host software has requested that the socket be powered

at an invalid voltage.

0 = Normal operation (default)

1 = Invalid VCC request by host software