- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄359234 > MT90503AG (ZARLINK SEMICONDUCTOR INC) CLIP, STRAIN RELIEF, 50WAY; For use with:820 Series Tripolarized Wiremount Sockets; Ways, No. of:50; Material:Metal; Connector type:Strain Relief RoHS Compliant: Yes PDF資料下載

參數(shù)資料

| 型號(hào): | MT90503AG |

| 廠商: | ZARLINK SEMICONDUCTOR INC |

| 元件分類(lèi): | 數(shù)字傳輸電路 |

| 英文描述: | CLIP, STRAIN RELIEF, 50WAY; For use with:820 Series Tripolarized Wiremount Sockets; Ways, No. of:50; Material:Metal; Connector type:Strain Relief RoHS Compliant: Yes |

| 中文描述: | ATM SEGMENTATION AND REASSEMBLY DEVICE, PBGA503 |

| 封裝: | 40 X 40 MM, 2.33 MM HEIGHT, PLASTIC, MS-034, BGA-503 |

| 文件頁(yè)數(shù): | 28/233頁(yè) |

| 文件大小: | 1341K |

| 代理商: | MT90503AG |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)當(dāng)前第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)第158頁(yè)第159頁(yè)第160頁(yè)第161頁(yè)第162頁(yè)第163頁(yè)第164頁(yè)第165頁(yè)第166頁(yè)第167頁(yè)第168頁(yè)第169頁(yè)第170頁(yè)第171頁(yè)第172頁(yè)第173頁(yè)第174頁(yè)第175頁(yè)第176頁(yè)第177頁(yè)第178頁(yè)第179頁(yè)第180頁(yè)第181頁(yè)第182頁(yè)第183頁(yè)第184頁(yè)第185頁(yè)第186頁(yè)第187頁(yè)第188頁(yè)第189頁(yè)第190頁(yè)第191頁(yè)第192頁(yè)第193頁(yè)第194頁(yè)第195頁(yè)第196頁(yè)第197頁(yè)第198頁(yè)第199頁(yè)第200頁(yè)第201頁(yè)第202頁(yè)第203頁(yè)第204頁(yè)第205頁(yè)第206頁(yè)第207頁(yè)第208頁(yè)第209頁(yè)第210頁(yè)第211頁(yè)第212頁(yè)第213頁(yè)第214頁(yè)第215頁(yè)第216頁(yè)第217頁(yè)第218頁(yè)第219頁(yè)第220頁(yè)第221頁(yè)第222頁(yè)第223頁(yè)第224頁(yè)第225頁(yè)第226頁(yè)第227頁(yè)第228頁(yè)第229頁(yè)第230頁(yè)第231頁(yè)第232頁(yè)第233頁(yè)

MT90503

Data Sheet

28

Zarlink Semiconductor Inc.

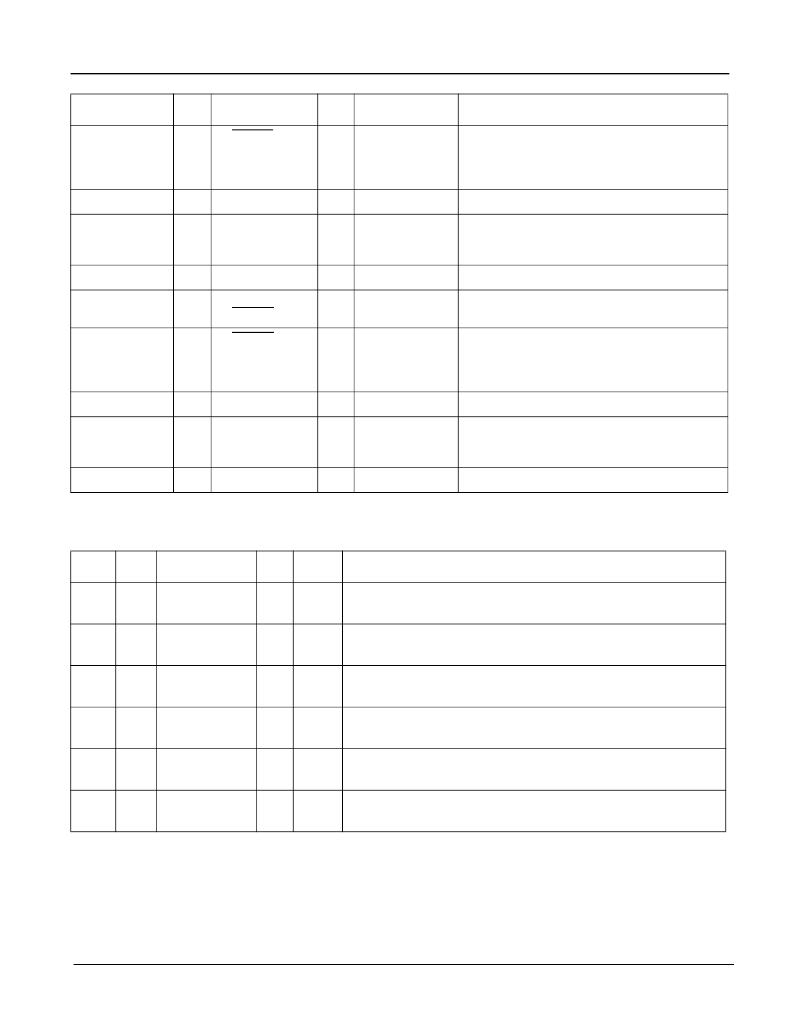

AF10

1. Z

2. Z

1. txc_enb

2. txc_clav

1.O

2.O

4 mA (F)

1. UTOPIA Port C TX Enable (in ATM). This pin

must be pulled-up externally.

2. UTOPIA Port C TX Cell Available (in PHY).

This pin must be pulled-down externally.

AH9

Z

txc_soc

O

4 mA (F)

UTOPIA Port C TX Start of Cell

AG9, AF9, AE9,

AH8, AG8, AF8,

AE8, AH7

Z

txc_data[7:0]

O

4 mA (F)

UTOPIA Port C TX Data bus

AG7

Z

txc_par

O

4 mA (F)

UTOPIA Port C TX Parity

AH6

1. rxc_clav

2. rxc_enb

1.I

2.I

TTL (F)

1. UTOPIA Port C RX Cell Available (in ATM)

2. UTOPIA Port C RX Enable (in PHY)

AJ6

1. Z

2. Z

1. rxc_enb

2. rxc_clav

1.O

2.O

4 mA (F)

1. UTOPIA Port C RX Enable (in ATM). This pin

must be pulled-up externally.

2. UTOPIA Port C RX Cell Available (in PHY).

This pin must be pulled-down externally.

AG6

1.Z

rxc_soc

I

TTL (F)

UTOPIA Port C RX Start of Cell

AF6, AE6, AF5,

AF4, AE2, AE3,

AF3, AD1

rxc_data[7:0]

I

TTL (F)

UTOPIA Port C RX Data bus

AH10

rxc_par

I

TTL (F)

UTOPIA Port C RX Parity

Pin

rst

Name

I/O

Type

Description

J25

pllvss_110

I

VSS pin for the CT PLL. See Figure 5, “PLL Pin Connections,”

on page 34 for recommended connections.

F28

Pllvdd_110

I

VDD pin for the CT PLL. See Figure 5, “PLL Pin Connections,”

on page 34 for recommended connections.

H26

Plllp2_110

I

Loop-filter pin for the CT PLL. See Figure 5, “PLL Pin

Connections,” on page 34 for recommended connections.

G28

pllagn_110

O

Analog Ground pin for the CT PLL. See Figure 5, “PLL Pin

Connections,” on page 34 for recommended connections.

AC5

pllvss_300

I

VSS pin for the FC PLL. See Figure 5, “PLL Pin Connections,”

on page 34 for recommended connections.

AG3

pllvdd_300

I

VDD pin for the FC PLL. See Figure 5, “PLL Pin Connections,”

on page 34 for recommended connections.

Table 9 - Phase Lock Loop (PLL) Pins

Pin

rst

Name

I/O

Type

Description

Table 8 - UTOPIA Interface Pins (continued)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MT90520 | 8-Port Primary Rate Circuit Emulation AAL1 SAR |

| MT90520AG | 8-Port Primary Rate Circuit Emulation AAL1 SAR |

| MT9072 | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| MT9072AB | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| MT9072AV | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MT90520 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:8-Port Primary Rate Circuit Emulation AAL1 SAR |

| MT90520AG | 制造商:Microsemi Corporation 功能描述:ATM SAR 2.048MBPS 2.5V CBR 456BGA - Trays |

| MT90520AG2 | 制造商:Microsemi Corporation 功能描述:ATM SAR 2.048MBPS 2.5V CBR 456BGA - Trays 制造商:Zarlink Semiconductor Inc 功能描述:ATM SAR 2.048MBPS 2.5V CBR 456BGA - Trays |

| MT90528 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:28-Port Primary Rate Circuit Emulation AAL1 SAR |

| MT90528AG | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:28-Port Primary Rate Circuit Emulation AAL1 SAR |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。