- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄370782 > HYB18T256324F-20 (INFINEON TECHNOLOGIES AG) 256-Mbit GDDR3 DRAM [600MHz] PDF資料下載

參數(shù)資料

| 型號(hào): | HYB18T256324F-20 |

| 廠商: | INFINEON TECHNOLOGIES AG |

| 英文描述: | 256-Mbit GDDR3 DRAM [600MHz] |

| 中文描述: | 256兆GDDR3顯示內(nèi)存[600MHz的] |

| 文件頁(yè)數(shù): | 29/80頁(yè) |

| 文件大?。?/td> | 2026K |

| 代理商: | HYB18T256324F-20 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)當(dāng)前第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)

HYB18T256324F–[16/20/22]

256-Mbit DDR SGRAM

Functional Description

Data Sheet

29

Rev. 1.11, 04-2005

10292004-DOXT-FS0U

3. The ODT disable function disables all terminators on th device.

4. If the user activates bits in an extended mode register in an optional field, either the optional field is activated

(if option implemented on the device) or no action is taken by the device (if ioption not implemented).

5. WR (write recovery time for write with autoprecharge) in clock cycles is calculated by dividing tWR (in ns) and

rounding up to the next integer (WR[cycles]=tWR[ns]/tCK[ns]). The mode register must be programmed to this

value.

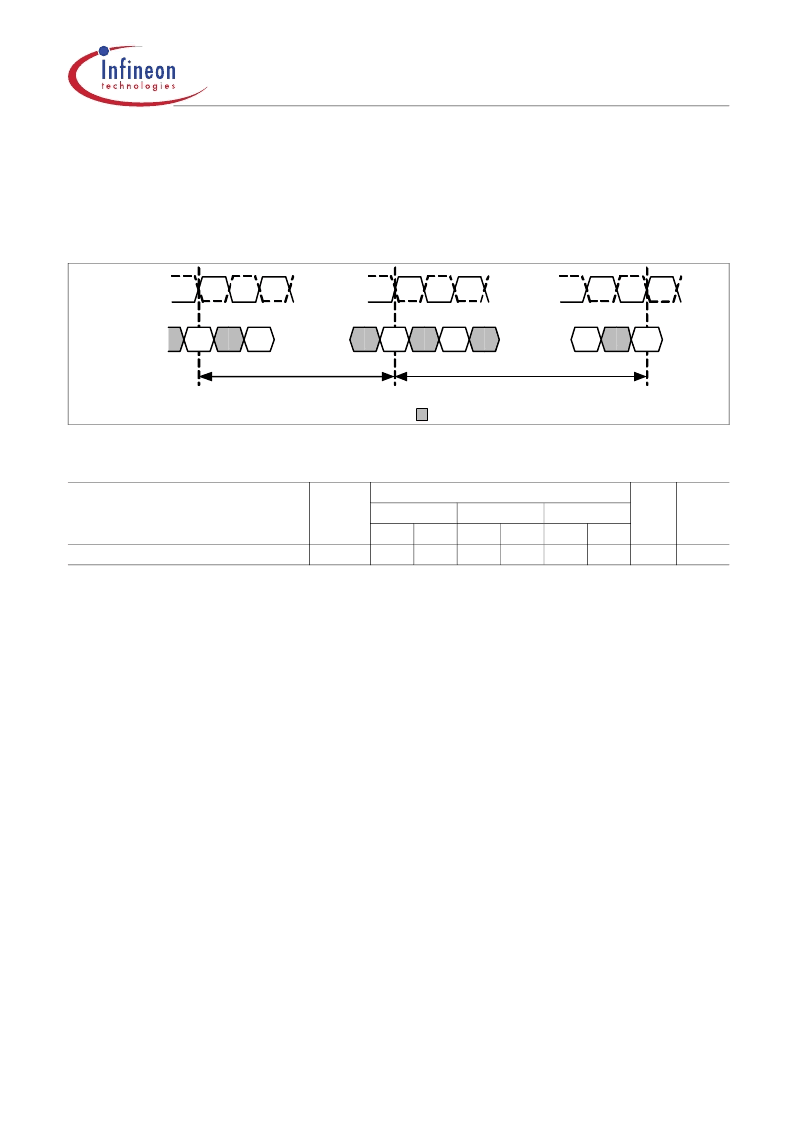

Figure 12

Extended Mode Register Set Timing

3.4.1

The DLL must be enabled for normal operation. DLL enable is required during power-up initialization and upon

returning to normal operation after having disabled the DLL. (When the device exits self-refresh mode, the DLL is

enabled automatically). Anytime the DLL is enabled, 200 cycles must occur before a READ command can be

issued.

DLL enable

3.4.2

The WR parameter is programmed using the register bits A4 and A5. This integer parameter defines as a number

of clock cycles the Write Recovery time in a Write with Autoprecharge operation.

The following inequality has to be complied with : WR * t

CK

≥

t

WR

, where t

CK

is the clock cycle time as defined in

Table 8

and t

WR

the Write Recovery time as defined in

Table 23

.

Note:Refer to

Figure 3.7.4

for more details.

WR

3.4.3

The data termination, Rtt , is used to set the value of the internal terminaton resistors. The GDDR III DRAM

supports ZQ / 4 and ZQ / 2 termination values. The termination may also be disabled for testing and other

purposes.

Termination Rtt

3.4.4

The Output Driver Impedance extended mode register is used to set the value of the data output driver impedance.

When the autocalibration is used, the output driver impedance is set nominally to ZQ / 6.

Output Driver Impedance

Table 16

Parameter

EMRS Timing Parameters for –1.6, –2.0 and –2.2 speed sorts

Symbol

Limit Values

–2.0

min

4

Unit

Notes

–1.6

–2.2

min

5

max

—

max

—

min

4

max

—

Mode Register Set cycle time

t

MRD

t

CK

#,+

#,+

$ONgT#ARE

0!

%-23

./0

!#

./0

T

20

T

-2$

#OMMAND

%-23%XTENDED-23COMMAND

0!02%!,,COMMAND

!#!NYCOMMAND

./0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HYB18T256324F-22 | 256-Mbit GDDR3 DRAM [600MHz] |

| HYB18T256400AFL-3 | 256 Mbi t DDR2 SDRAM |

| HYB18T256160A-3S | 256 Mbi t DDR2 SDRAM |

| HYB18T256800AFL-3 | 256 Mbi t DDR2 SDRAM |

| HYB18T256400AFL-37 | 256 Mbi t DDR2 SDRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HYB18T256400AF-3.7 | 制造商:Infineon Technologies AG 功能描述:64M X 4 DDR DRAM, 0.5 ns, PBGA60 |

| HYB18T256400AF-5 | 制造商:Infineon Technologies AG 功能描述:SDRAM, DDR, 64M x 4, 60 Pin, Plastic, BGA |

| HYB18T256800AF-5 | 制造商:Infineon Technologies AG 功能描述: |

| HYB18T512161BF-25 | 制造商:Qimonda 功能描述:SDRAM, DDR, 32M x 16, 84 Pin, Plastic, BGA |

| HYB18T512400AF-5 | 制造商:Intersil Corporation 功能描述:SDRAM, DDR, 128M x 4, 60 Pin, Plastic, BGA |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。