- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371187 > TMXF84622 TMXF84622 155 Mbits/s/622 Mbits/s Interface SONET/SDH x84/x63 Ultramapper PDF資料下載

參數(shù)資料

| 型號: | TMXF84622 |

| 英文描述: | TMXF84622 155 Mbits/s/622 Mbits/s Interface SONET/SDH x84/x63 Ultramapper |

| 中文描述: | TMXF84622 155 Mbits/s/622 Mbits /秒接口的SONET / SDH x84/x63 Ultramapper |

| 文件頁數(shù): | 36/62頁 |

| 文件大小: | 902K |

| 代理商: | TMXF84622 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁當前第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁

36

Agere Systems Inc.

Advance Data Sheet, Rev. 2

July 2001

SONET/SDH x84/x63 Ultramapper

TMXF84622 155 Mbits/s/622 Mbits/s Interface

3 Pin Information

(continued)

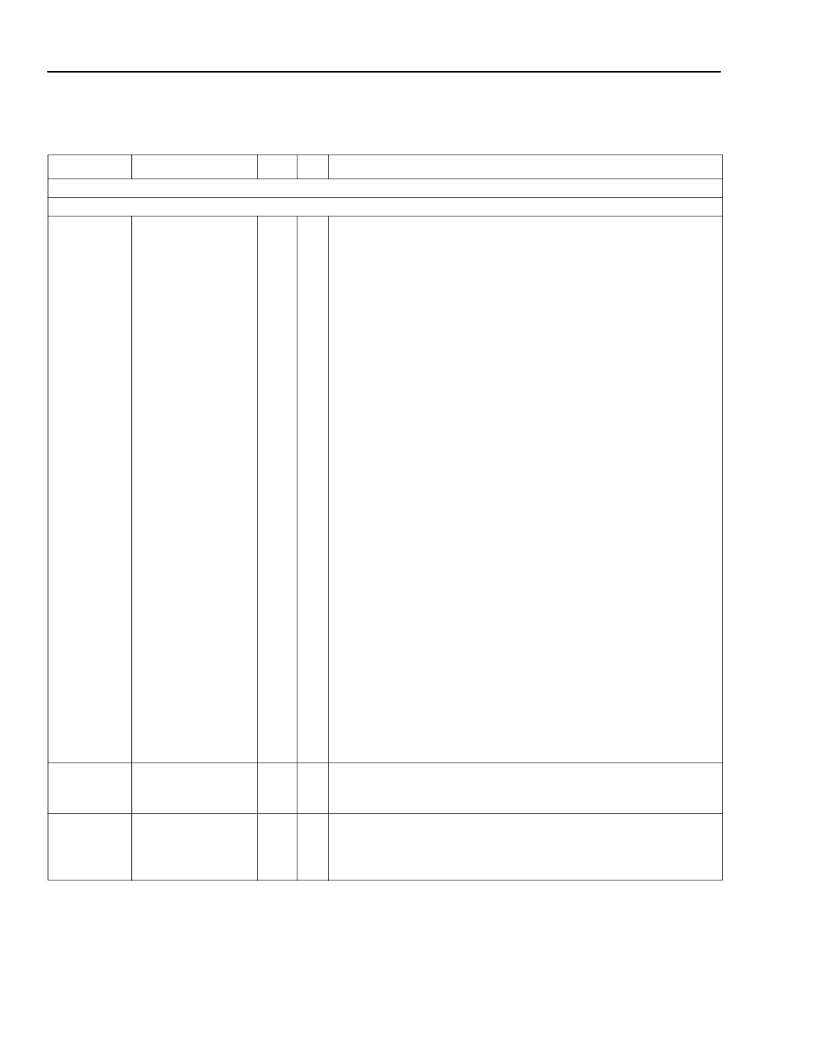

Table 1. Pin Descriptions

(continued)

Pin

* O

1

indicates external pull-up recommended (unused or system required),

I/O

2

indicates external pull-down recommended (unused or system required),

I

D

; I/O

D

indicate internal pull-down, I

U

indicates internal pull-up.

Receive path convention is away from the high-speed fiber output. Note that CHITX signals are labeled Transmit, as seen from the cross con-

nect perspective.

Symbol

Type I/O

*

Description

Multifunction System Interface

(continued)

CHI Receive Path Direction (44 total, last 2 not indexed)

CHITXDATA[42:1]

—

I/O

Configurable Outputs from the Internal Cross Connect.

AA33, Y29,

AB34,

AA32,

AB33,

AA30,

AC34,

AA29,

AC33,

AD34,

AC32,

AB29,

AD33,

AE34,

AD32,

AC30,

AF34, AE33,

AC29,

AD30,

AG34,

AF33, AF32,

AH34,

AD29,

AG33,

AG32,

AE29, AJ34,

AF30, AF29,

AH33,

AK34, AJ33,

AG30,

AM34,

AJ30, AJ29,

AK29,

AP32,

AN31, AJ27

AA34

Switching modes:

CHI: Transmit system data or data and signaling output

(2.048 Mbits/s, 4.096 Mbits/s, 8.192 Mbits/s, or 16.384 Mbits/s).

Parallel system bus:

CHITXDATA[16:1]: Transmit system data bus output is restricted

to the first 16 outputs (19.44 Mbits/s). MSB

—

CHITXDATA[16] through LSB to CHITXDATA[1].

CHITXDATA[42:17]: Not used in PSB mode only.

Transport modes:

Framer

—

LIU: Transmit negative-rail DS1/E1 line data output or

8 K frame sync output.

VT mapper: 8 K sync output for DS1/E1 or 2 K sync output for VC.

M12:

CHITXDATA [7:1]: Carry DS2 data output from the M12 MUX.

CHITXDATA [14:8]: Carry DS2 clock input/output of the M12 MUX.

CHITXDATA [21:15]: Carry DS2 data input to the M12 deMUX.

CHITXDATA [28:22]: Carry DS2 clock input to the M12 deMUX.

CHITXGFS

—

I

CHI:

Transmit system frame sync input.

Parallel system bus: Transmit system frame sync input.

Switching Modes:

CHI: Transmit global system clock input

(4.096 MHz, 8.192 MHz, or 16.384 MHz).

Y30

CHITXGCLK

—

I

Parallel system bus: Transmit global clock input (19.44 MHz).

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TN2-L-H-3V | SLIM POLARIZED RELAY |

| TN2-L-H-48V | SLIM POLARIZED RELAY |

| TN2-L-H-4V | SLIM POLARIZED RELAY |

| TN2-L-H-5V | SLIM POLARIZED RELAY |

| TN2-L-H-6V | SLIM POLARIZED RELAY |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TMXF846221BL-3-DB | 制造商:LSI Corporation 功能描述:Mapper DS3/E3/DS2/DS1/DS0/E1 SONET/SDH 155Mbps/622Mbps 1.5V/3.3V 700-Pin BGA Bag |

| TMXM-0-49 | 制造商:Brady Corporation 功能描述: |

| TMXM-11 | 制造商:Brady Corporation 功能描述: |

| TMXM-1-10-PK | 制造商:Brady Corporation 功能描述:MICRO CONSECUTIVE NOS. REPEAT - LEGEND: 1-10 |

| TMXM-1-25-PK | 制造商:Brady Corporation 功能描述:MICRO CONSECUTIVE NOS. REPEAT - LEGEND: 1-25 |

發(fā)布緊急采購,3分鐘左右您將得到回復。